用OpenCV和Vivado HLS加速基于Zynq SoC的嵌入式视觉应用开发

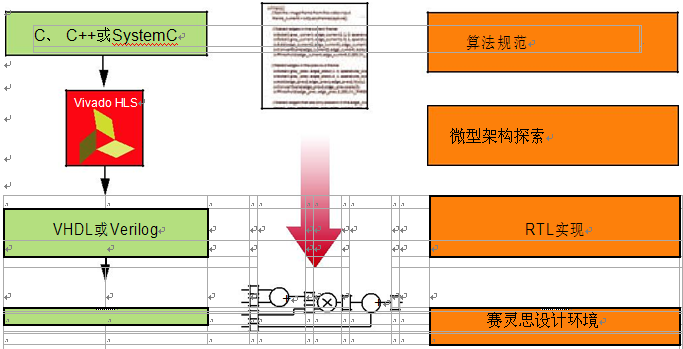

关重要。 图2 高层次综合设计流程 为了进一步帮助嵌入式视觉开发人员创建Smarter Vision系统,赛灵思在Vivado中增加了对OpenCV计算机视觉算法库的支持。赛灵思还推出了最新IP Integrator工具和SmartCORE™ IP以支持此类设计。 OPENCV推广计算机视觉技术 OpenCV开辟了一条开发智能计算机视觉算法的途径,而且能预测实时性能。该库为设计人员提供了用于算法试验和快速原型设计的环境。 OpenCV设计框架得到多平台支持。不过在许多情况下,要提高库对嵌入式产品的效率,就需要在嵌入式平台上实现,而且该平台要能够加速高强度例程,满足实时性能要求。 虽然OpenCV在设计时就考虑到计算效率问题,不过它源自传统计算环境,可支持多核处理。这种计算平台或许对高度强调效率、成本和功耗的嵌入式应用来说并不是最佳选择。 OPENCV的特性 OpenCV是一款基于BSD许可证授权发行的开源计算机视觉库,这就意味着它可免费用于学术和商业应用中。它最初设计旨在提高通用多处理系统的计算效率,侧重于实时应用。此外,OpenCV还提供C/C++和Python等多种编程接口。 开源项目的优势在于,用户能持续改进算法,并将算法扩展用于多种不同应用领域。目前用OpenCV可现实2,500多种功能,其中包括: • 矩阵数学 • 公用设施和数据结构 • 通用图像处理功能 • 图像转换 • 图像金字塔 • 几何描述符函数 • 特性识别、提取和跟踪 • 图像分割与拟合 • 摄像头校准、立体化和3D处理 • 机器学习:检测、识别 图3 OpenCV算法库开发的运动检测应用实例 用HLS加速OPENCV函数 一旦完成了嵌入式视觉系统架构的分区,找到了计算强度最大的部分,HLS工具就能帮助您加速这些函数,同时仍能继续使用C++编写。Vivado HLS用C、C++或SystemC代码生成高效的RTL实现方案。 此外,以IP为中心的Vivado设计环境提供丰富的处理IP SmartCORE,能简化到图像传感器、网络及其它必要I/O接口的连接,简化OpenCV库中这些函数的实现。这相对于其它实现方案而言是一种明显的优势,因为其它方案哪怕是最基本的OpenCV I/O功能都需要加速。 为什么需要高层次综合? 赛灵思推出的Vivado HLS是一款软件编译器,旨在将C、C++或SystemC编写的算法转变为针对用户定义时钟频率和赛灵思产品系列器件优化的RTL。在C/C++程序解释、分析和优化方面,它与x86处理器的编译器具有相同的核心技术基础。这种相似性有助于从台式机开发环境快速移植到FPGA实现。您选择目标时钟频率和器件后,无需用户输入,Vivado HLS会默认生成RTL实现。此外,Vivado HLS与其它任何编译器一样,也分不同的优化级别。由于算法最终执行目标是定制的微型架构,因此Vivado HLS可实现的优化级别比传统的编译器具有更精细的粒度。传统的针对处理器的软件设计O1 – O3优化理念被架构探索要求所取代,这些要求与用户技术相结合,指导Vivado HLS创建尽可能出色的实现方案,满足特定算法的功耗、面积占用和性能要求。 图4 Zynq SoC上采用ARM处理器的运动检测 图2给出了HLS编译器的用户设计流程。从理念上讲,用户提供C/C++/SystemC算法描述,编译器就能生成RTL实现。程序代码转化为RTL的过程分为四大阶段:算法规范、微型架构探索、RTL实现和IP封装。 算法规范阶段是指将针对FPGA架构的软件应用开发。该规范可在标准桌面软件开发环境中,全面利用赛灵思提供的OpenCV等软件库进行开发。除了支持以软件为中心的开发流程外,Vivado HLS还提升了从RTL到C/C++的提取验证速度。用户能用原软件进行全面的算法功能验证。通过Vivado HLS生成RTL后,生成的设计代码类似于传统软件编译器生成的处理器汇编代码。用户可在汇编代码级进行调试,但这一步并不是必需的。 虽然Vivado HLS能处理几乎所有针对其它软件编译器的C/C++代码,但代码有一个限制。在用Vivado HLS编译代码到FPGA过程中,用户代码不能包含任何运行时动态存储器分配。与算法绑定于单个存储器架构的处理器不同,FPGA实现采用特定算法的存储器架构。通过分析阵列和变量的使用模式,Vivado HLS能确定哪些物理存储器布局和存储器类型最适合算法的存储和带宽要求。这种分析工作的唯一要求就是在C/C++代码中明确描述算法使用的所有存储器阵列。 从C/C++转为优化的FPGA实现的第二步就是微型架构探索。在这一阶段,您可运用Vivado HLS编译器优化来测试不同的设计,以找到适当的面积和性能组合。您可在不同性能点实现相同的C/C++代码,无需修改源代码。Vivado HLS编译器优

赛灵思 Vivado OpenCV Smarter SoC 相关文章:

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)