全面剖析数字电路中的复位设计

dule_rst_b)

if(!module_rst_b) data_q <= 1’b0;

else data_q <= data_d;

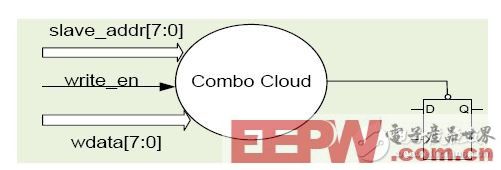

在上面的示例中,slave_addr,write_enable和wdata改变它们的值 w.r.t system clock,使用静态时序分析,设计人员可以保证在目标触发器的设置时间窗口之前这些信号在一个时钟周期内的稳定性。然而,在该示例中,这些信号直接用作触发器的异步清零输入。

因此,即使在特定的时间slave_addr[7:0]在逻辑上将其值从“00000110”改为 “01100000”,但由于组合逻辑的传播延迟(净延迟和信元延迟)它可以用一个序列“00000110 --> 00000010 --> 00000000 --> 01000000 --> 01100000”生成过渡。

在这段时间里,salve_addr为“00000010”,如果wdata[7:0]始终为零且“write_enable” 已经被断言,那么它将在module_rst_b创建一个无用脉冲,从而导致虚假复位。

图6:复位路径的组合逻辑

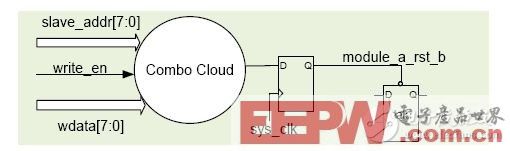

2. 解决方案

首先注册组合输出,然后再将其用作复位源(如图7所示)。

图7:复位路径的组合逻辑解决方案

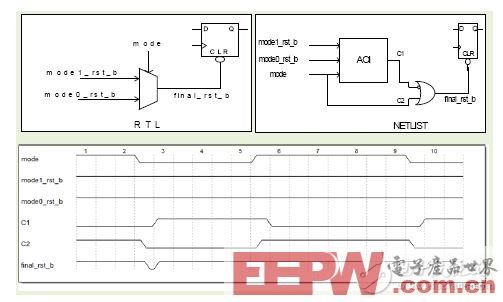

3. 问题(II)

在上面的示例中,复位路径的组合逻辑解决方案并不完善。如果组合逻辑输入大约在同一时间发生变化,那么它可能在设计中触发虚假复位。然而,如果组合逻辑的输入信号变化相互排斥,那么它可能不会引起任何设计问题。例如,测试模式和功能模式相互排斥。因此复位路径的测试复用是有效的设计实践。

然而,对于某些情况,变化相互排斥的静态信号或信号可能会导致设计出现虚假复位触发。下面的示例描述了此类设计可能出现问题。

图8:复位路径的组合逻辑(问题 2)

在上面的示例中,多路复用结构用于复位路径,同时进行RTL编码。其中“mode” 是一个控制信号,不频繁改变,而mode0_rst_b和mode_1_rst_b是两个复位事件,然而在合成RTL时,在门控级它被分解成不同的复杂的组合(And-Or-Invert[AOI])信元。虽然在逻辑上它相当于一个多路复用器,但由于不同的信元和净延迟,每当信号“mode”从 1-->0变化时,final_rst_b都会产生干扰。

4. 解决方案

* 在合成过程中在复位路径保留多路复用结构,因为多路复用结构与其他组合逻辑相比易于产生干扰。MUX Pragma可以在编码RTL时使用,这将有助于合成工具在复位路径中保留任何多路复用器。

设计中的同步复位问题

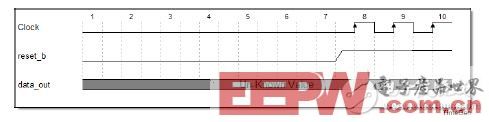

1. 问题(I)

在许多地方,设计人员在时钟方面喜欢同步复位设计。原因可能是为了节省一些芯片面积(带有异步复位输入的触发器比任何不可复位触发器都大)或让系统与时钟完全同步,也可能有一些其他原因。对于此类设计,当复位源被断言时需要向设计的触发器提供时钟,否则,这些触发器可能会在一段时间内都不进行初始化。但当该模块被插入一个系统时,系统设计人员可能选择在复位阶段禁用其时钟(如果在一开始不需要激活该模块),以节省整个系统的动态功耗。因此,该模块甚至在复位去断言后一段时间内都不进行初始化。如果该模块的任何输出直接在系统中使用,那么将捕获未初始化和未知的值(X),这可能会导致系统功能故障。

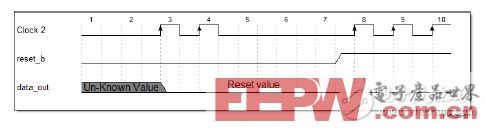

图9:同步复位问题时序图

2. 解决方案

在复位阶段启用该模块的时钟且持续最短的时间,使该模块内的所有触发器都在复位过程中被初始化。 当系统复位被去断言时,模块输出不会有任何未初始化的值。

图10:同步复位问题已解决

3. 问题(II)

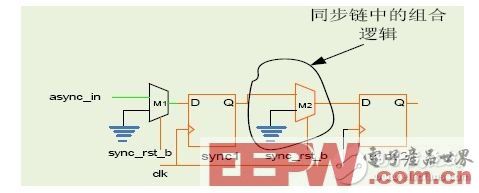

在时钟域交叉路径使用两个触发同步器是常见做法。然而,有时设计人员对这些触发器使用同步复位。相同的RTL代码是

always @(posedge clk )

if(!sync_rst_b) begin

sync1 <= 1‘b0; sync2 <= 1’b0 ;

end

else begin

sync1 <= async_in; sync2 <= sync1

end

在硬件中进行了RTL合成后,上面的代码会在双触发器同步器的同步链中引入组合逻辑,这会带来风险,并缩短sync2触发器输入进入亚稳态的时间。

图11:同步复位问题2

4. 解决方案

可用以下方式编写RTL代码,以避免同步链的组合逻辑。

always @(posedge clk )

if(!sync_rst_b) begin

sync1 <= 1‘b0;

end

else begin

sync1 <= async_in; sync2 <= sync1

end

在上面的代码中,对sync2触发器不使用复位,因此在同步链中不会实现组合信元。然而,需要注意sync2需要一个额外的周期才能复位,这不应导致设计出现任何问题。

冗余复位同步器引起的问题

1. 问题

在使用多个异步时钟的设计中,设计人员需要确保在目标寄存器使用的时钟方面,异步复位的同步去断言,否则可能导致目标触发器发生时序违反,从而产生

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)