基于DaVinci?平台的网络视频解码系统分析与设计

行视频信号后,先根据预定好的分时传输协议中解出6路单独的视频信号,分别放置在DDR的不同区域中;完成6路视频的缓存和仲裁后,根据系统的需求对视频数据进行DMA操纵,通过PCI-E设备把视频数据送入系统进行显示。

3 硬件设计

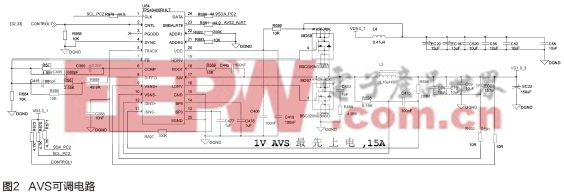

DM816X模块的硬件电路主要由主芯片816X、4片DDR3、Fash、网络PHY片和电源模块组成组成。网络PHY芯片采用Mirel的KSZ9031,该芯片体积小、功能全、支持速率自适应、双绞/直连线调节功能。该芯片和DM816X的EMAC(Ethernet Media Access Controller)口直接连接,把网络数据接入到DM816X。主芯片外部挂有4片DDR3,主要用做816X的内存映射空间和视频处理的缓冲区域,可以在软件小系统中进行自由配置。同时,主芯片外部还带一个Nand Flash,用于存储引用程序和系统文件。在芯片外围,根据应用需要放置硬件配置电路,把系统配置成网络启动。因为芯片对电源的精度和上电时序均有严格要求,因此专门针对该芯片设计了上电时序电路和AVS可调电源。芯片的上电时序要求为3.3V>1V AVS>1V Constant>1.8V>1.5V>0.9V,为此,采用了专用时序控制芯片LM3881MM对上电时序进行了控制。主芯片因为采用了先进的制造工艺,其核心电压1V AVS对应每个芯片均有一个精准值,在芯片运行过程中,也会因为工作状态而调整核心电压,所以针对该电压也设计了专门的可调电源供电电路[4],具体电路模块见图2。图2中,电源芯片采用TPS40400,其输出端通过反馈电路送回反馈管脚,芯片带有IIC的Slave模块,连接到816x主芯片。在上电开始后,主芯片会读取相关寄存器,反馈给电源芯片具体的电源调整精准值;在系统运行过程中,如果同时开启了3个解码核,会使得芯片功耗需求增加,主芯片也可以通过IIC通讯通知电源芯片调整电源输出。

FPGA硬件电路模块实现相对简单,主要包括了PCI-E接口的FPGA芯片、DDR2、存储Flash、JTAG接口和电源模块。逻辑芯片采用ALTER的A7系统芯片,采用SPI加载逻辑的方式进行加载,外挂4片DDR2使用两个控制器对视频数据进行缓存。JTAG接口主要用于逻辑程序调试。操作系统端连接采用PCI-E接口,由逻辑芯片内存自带的PCI-E硬核实现。

4 DM816X软件设计

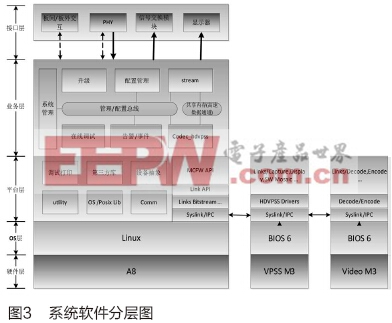

为了便于软件功能的移植、替换、添加和删除,整个软件采用层次式和模块化的软件结构。纵向分布由5个层次组成,从下向上,分别是硬件层、OS层、平台层、业务层、接口层。横向分布由3个子系统构成,从左至右,依次是A8核子系统、HDVPSS M3核子系统、Video M3核子系统,具体结构见图3。

硬件层是软件系统运行的硬件平台,其核心是TMS320数字多媒体处理器,由A8、HDVPSS M3、Video M3、DSP 4个核构成,其中HDVPSS M3、Video M3核是M3核。本软件没有使用到DSP核,所以硬件层由A8、HDVPSS M3、Video M3 3个核构成。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

OS层是硬件层上的操作系统层,由Linux、BIOS 6两个操作系统构成。Linux运行A8核上,BIOS 6运行在M3核[5]。

平台层运行在操作系统层上,屏蔽软硬件复杂性,抽象业务层所需要的功能接口,向上支撑业务层。基于A8核的平台层由调试打印、第三方库、设备抽象、utility、OS/Posix Lib、Comm以及MCFW多通道框架接口构成。MCFW是TI提供的一套用来处理多媒体视频的接口。A8核端由Syslink/IPC、Link Bitstream、Link API、MCFW API组成。VPSS M3核端由Syslink/IPC、HDVPSS Drivers、Links Capture/Display/SW Mosaic组成。Video M3核由Syslink/IPC、Decode/Encode、Links Decode/Encode组成。核与核之间的数据交互由Syslink/IPC实现。816X是一个多核SOC设备,各个核之间的通信需要通过软件设计来实现。芯片的主处理器是A8,A8核端的Link API用来创建、控制、连接Links。通常由该处理器引导加载各个从处理器,包括了Video-Media Controller,VPSS-Media Controller等。其中解码核实由Video-Media Controller负责管理的。引导加载过程包括从处理器的电源管理,复位控制,在合适的寄存器中写入从处理器执行的入口点。为了有效地实现多核通信,软件还充分利用了邮箱中断和自旋锁功能实现。Mailbox为处理器通过写寄存器,向其他处理发送中断机制。A8,Media Controller等之间通过系统级的Mailbox进行通信。3个HD VICP2S的IP模块有各自独立的邮箱。SOC通过自旋锁[6](SpinLock)方便实现了系统共享资源的互斥。

业务层由系统管理、在线升级、配置管理、stream、在线调试、告警/事件、codec_hdvpss几个模块组成。管理/配置总线用来实现业务层模块间的通信,共享内存(高速

DaVinci IP视频 CPU Linux FPGA 201411 相关文章:

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 什么是达芬奇(DaVinci)技术(12-07)

- Blackfin助您无线IP视频监控的应用(06-24)

- DSP 在数字视频处理技术中的应用(07-16)

- Nut/OS和μC/OS—II的实时调度算法比较 (04-07)