基于SOPC的通用型JTAG调试器的设计

。一个片上系统就基本包含了在线仿真器的绝大部分功能,任何硬件结构设计的变化都在该片FPGA上,这使得通用在线仿真器这个概念得以实现。对其他芯片在线仿真,只需更改ARM7TDMI JTAG IPcore模块,重新下载到FPGA中,便可以对另一种处理器芯片进行在线仿真。该IPcore用Verilog语言实现,保存为armjtag.v文件。通过Quartus II里的SOPC Builder可以将该文件生成组件,再将其加入Nios系统中。器件引脚分配好后,就在Quartus II里全编译,最后生成ice.pof文件。将该文件通过编程器烧写到配置芯片EPCS4里面。这样硬件系统就完成了。

2.2 软件设计与实现

本系统的软件部分包括2个模块:一是PC端的开发调试界面,二是调试器里面的控制程序。2个模块通过TCP/IP协议通信。

PC端开发调试界面的主要功能是接收用户的调试命令,并显示调试结果。这是系统与用户进行交互的唯一方式。开发调试界面对上给用户提供统一的调试功能接口,对下给调试器提供统一的调试命令。本系统使用VisualC++开发。

调试器里的控制程序主要功能是将上层用户调试命令转换成特定的JTAG指令序列,并控制IPcore将其发送出去,同时接收JTAG反馈信息并发送回用户界面。本系统使用Nios IDE来开发。在Nios IDE的工程属性中加入LwIP和μC/OS组件。主程序首先初始化μC/0S,初始化LwIP协议栈,再启动μC/OS。所有程序控制放在μC/OS的OSStart()任务里。该任务首先建立一个套接字,然后在死循环中等待数据到来。当收到来自PC端的调试命令后,从数据包中分离出命令字和参数,将命令字转换成IPcore需要的调试命令,通过Avalon总线将其发送到IPcore,并等待IPcore工作完成。最后将IPcore传回的数据打包发回PC端。

目前提供的通用调试命令如表1所列。

在TCP/IP数据包中,有效数据为12字节。第1至4字节是命令代码,第5至8字节为命令参数1,第9到12字节为命令参数2。命令参数1和命令参数2是否有效取决于命令代码。主控制程序收到数据包后,将命令代码发往JTAG IPcore的指令端口地址,并根据命令代码向参数端口地址发送命令参数1。如果该命令代码需要命令参数2,则在下一个周期发送。

在SOPC的硬件系统设计中,所有的外设都是统一编址。将JTAG IPcore的指令端口地址和参数端口地址分别设置成0x00910850和0x00910860,端口位宽为32位。因此在程序里,往IPcore发送指令只需要往地址0x00910850写32位数据;往IPcore发送参数只需要往地址Ox00910860写32位数据。反馈数据端口地址设置成Ox00910870,端口位宽为32位。因此在程序里,读取JTAG反馈数据只需读取地址0x00910870的32位数据。

2.3 JTAG IPcore的实现

JTAG IPcore是本调试器的核心,下面简单介绍一下该部分的实现。

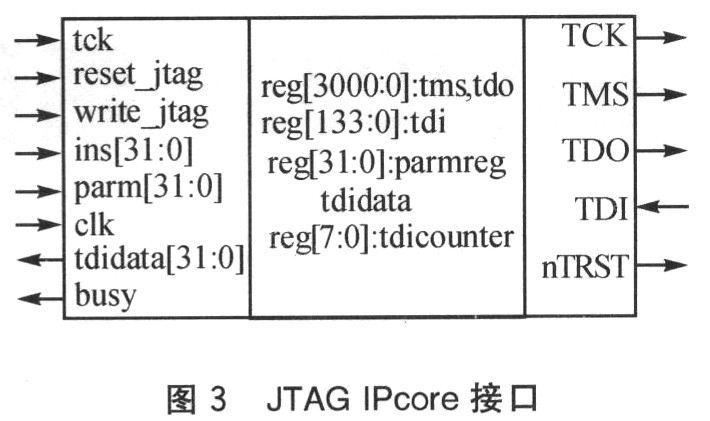

IPcore的接口如图3所示。

该IPcore的对外接口由两部分组成:一是与Avalon总线通信的接口部分,即图中的左边部分;二是与被调试CPU通信的接口部分,即图中的右边部分。另外,在整个实现中,定义了一些重要的寄存器。

“reg[3000:O]tms,tdo"分别用来存放完成当前操作的tms序列和tdo序列。像访问存储器这样的操作需要很长的tms序列和tdo序列,因此用了3001位。IPcore每次从这2个寄存器读取1位后,就向对应的引脚发送数据。tdi寄存器只用了134位,因为不是每个tdi输入对JTAG调试都有用。parmreg寄存器用来存放总线上传来的参数。tdidata寄存器用来存放从tdi引脚读取的有效数据,将被发送到Avalon总线。tdicolJnter寄存器用来对tdi输入数据计数。

Avalon总线上来的指令发送到ins[31:0]端口。在调试器主程序里判断指令,做出相应的动作。当IPcore读取到某个指令后,根据命令代码查找对应的TMS命令序列,找到以后将命令序列送到tms寄存器。同时,通过parm[31:O]端口读取命令参数,根据命令参数生成对应的TDO序列,将其送到tdo寄存器。当两个寄存器的内容准备好后,在TCK时钟的控制下,通过TMS引脚和TD0引脚分别串行输出。在TDO引脚输出的同时检测TDI引脚,并在适当时机将TDI引脚上的数据读入IPcore,经过处理后发送回总线。

由于TMS序列长度较长且其对应于各个调试命令是固定不变的,因此在本设计中,将TMS序列作成一个表,存放在IPcore里,而不是通过总线发送。需要时,根据不同的命令代码来读取。这样可以节约时间,提高调试速度。

结 语

本文介绍了一个基于SOPC的通用调试器的设计方案与实现过程。在开发过程中,IP复用、软硬件协同设计等先进的嵌入式设计思想对缩短开发时间、降低开发风险起到了很好的作用。同时,自主开发的ARM7TDMIJT

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 基于DSP和SOPC数字信号发生器的设计(01-05)

- 基于Linux的SoPC应用系统设计(04-23)

- 基于DSP的实时数据处理系统浅析(02-28)

- 基于LXI总线的1553B通讯模块设计与开发(11-24)

- 双MicroBlaze软核处理器的SOPC系统设计(01-27)