嵌入式开发技巧:利用编程技术发挥多内核架构优势

们有别于更传统的SMP或AMP平台。多年来在像索尼的PlayStation 3这样的基于Cell的平台上所作的软件改进突显了编程技术和经验的变化。

GPU等专用处理器

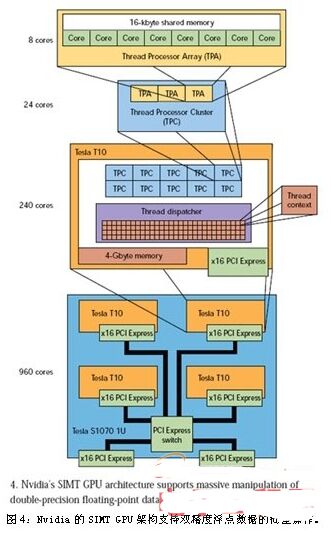

改变编程技术是使用图形处理单元(GPU)是否成功的关健。来自ATI和Nvidia等公司的GPU在单个芯片内有上百个内核,这些GPU可以被整合进多芯片解决方案,向开发人员提供上千个内核。例如,集成进1U机箱的4个Nvidia Tesla T10就可以提供960个内核(图4)。

对Tesla或其它任何兼容的Nvidia GPU芯片进行编程都极具挑战性,但类似Nvidia的CUDA这样的架构或基于CUDA的运行时利用可以使工作变得更加轻松。部分挑战来自于 Nvidia GPU的单指令、多线程(SIMT)架构。与许多高性能系统一样,这种GPU喜欢处理数组数据。对许多应用来说这是不错的选择,但并非都是这样,这正是 GPU经常要与多内核CPU匹配的原因之一。

另一种并行编程架构,CUDA和OpenCL(开放计算语言),则完全匹配GPU方法(使用与主处理器分开的存储器)。这意味着数据在能被操作之前必须从一个地方移动到另一个地方。C编程语言有一定扩展,但也有限制。例如,它是自由递归的,不支持函数指针。其中一些限制源自SIMT方法。

许多应用程序使用CUDA,但与传统SMP平台相比,性能增益有很大的变化,从2倍到100倍不等。造成这种变化的原因是,线程以32为组运行时的效率最高。分支不影响性能,前提是32线程组在同一分支内。

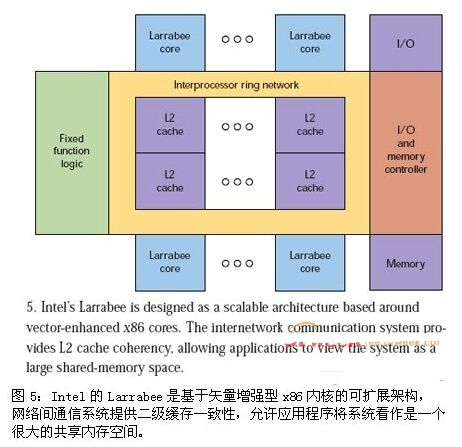

像GPU这样的专用处理器,其采用的方案是同时提供图形和多内核处理。另外一种方案是使用许多传统内核,如Intel的Larrabee(图5)。Larrabee使用专门针对矢量处理优化过的x86兼容内核。

从某种角度看,Larrabee有点类似于IBM的Cell处理器。Larrabee内核只有32KB的一级缓存和256KB的二级缓存可以访问。如果数据不在缓存中,必须从内存控制器或系统中的另一个缓存中申请,然后数据被放进内核的缓存中,再由应用程序继续处理。

环形总线用于内核和控制器之间的通信。IBM的Cell单元互连总线(EIB)也是一种环形总线,连接着 SPE和内存控制器以及外设接口。从编程角度看,Larabee的缓存和Cell的SRAM有很大的差异。诚然,对编程人员来说,Larrabee看起来更像是一组连贯缓存的x86处理器。由于其GPU定位,编程人员可以充分利用它对DirectX和OpenGL的支持。

多内核联网

多内核芯片也是网络基础设施中的常见元件。处理10Gps的网络对多内核芯片来说本身就是很大的挑战。分析和处理来自线速网络连接的数据需要大量的处理资源。

Netronome的NFP-3200网络流量处理器包含40个1.4GHz的内核,每个内核可以运行8个线程,因此1个芯片总共可提供320个基于硬件的线程。这个数量级与GPU相同,但这些处理器主要用于数据包处理。

与IBM的Cell一样,NFP-3200也有一个主CPU型控制器,而且是一个ARM11内核。NFP-3200的40个内核也叫做微引擎,兼容 Intel的IXP28xx架构,主要用于网络处理。这种兼容性很重要,因为大量代码是针对这种架构开发的。较老的芯片具有较少的内核,因此在某种意义上 NFP-3200提供的是相同解决方案。

当然,为解决问题而简单地采用更多的内核只是其中一种措施。Netronome作了大量改进,例如支持TCP任务卸载的增强型微模块。互连速度也更高了,内核之间的运行速度高达44Gbps。

Netronome芯片拥有大量的专用处理器,其中包括了用于处理各种安全协议的加密系统。Netronome的PCI Express接口支持x86处理器经常使用的I/O虚拟化功能。它能被移动到NFP-3200旁边,而不是被另外一条网络链路隔开。

与其它多内核芯片相比,编程NFP-3200通常没有太大问题,因为针对IXP28xx系列有大量现成代码。另外,Netronome提供库,这使得网络处理应用程序的创建更像是模块的堆叠。

Cavium的Octeon II是一种更传统的SMP多内核设计,有2到6个64位 MIPS64内核,它们通过一个交叉开关相连。与Netronome芯片一样,Octeon II是针对网络和存储设备设计的。

Octeon II还有一个RAID 5/6加速器以及用于数据包检查的正则表达式超有限时序机(HFA)。编程Octeon II与编程大多数SMP系统相仿。Octeon II可以运行诸如Linux的操作系统。

其它多内核架构

采用更激进的多内核架构会增加编程事务,但它能为开发人员开启利用新架构的机会。IntellaSys的SeaFORTH 40C18就属于这种类型(图6)。它本身的编程语言是VentrueForth,指令长度实际上是5位,4个指令可以压缩为单个18位的字(一个指令只有3位长)。40C18有40个内核,它们有相同的处理单元,并且都有64个字的RAM和64个字的ROM。

与具有更多存储空间的芯

- 革新2410D开发板试用手记(04-21)

- 建立针对arm-linux的交叉编译环境(02-07)

- 基于J2ME的无线网络应用开发(05-24)

- 多内核设计的三种设计模式概述(01-17)

- 基于LabVIEW的32位处理器嵌入式系统的开发(05-13)

- [跟我学嵌入式开发] 堆和栈(11-28)