Intel开发硬件加速器 AES加解密效率陡升

时间:09-12

来源:互联网

点击:

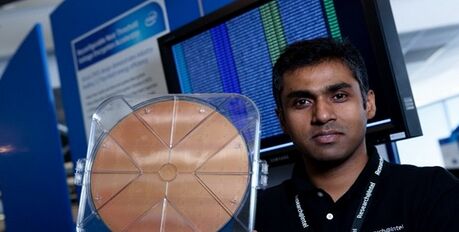

研究日上,Intel技术人员拿出了一块特殊的晶圆,声称是一种硬件加速器的原型,但却没有给出具体说明。其中到底蕴含着什么秘密呢?

我们知道,现代微处理器需要处理的数据量异常庞大,同时又必须维持较低的功耗。AES(高级加密标准)是一种计算密集型非常之高的分组密码,常用于高性能万亿次级别微处理器平台上的媒体内容保护、数据加密,但是实时媒体处理数据率的指数级增长、伽罗华域(Galois Field/有限域)算术映射的计算复杂性都对通用目的微处理器构成了严峻挑战,无论是功耗还是性能都在处理器核心内部遭遇了瓶颈。

于是Intel就开发了这种高效率的可配置特殊目的硬件加速器,专用于媒体内容的片内实时加密和解密。研究日上展示的原型晶圆和芯片采用45nm HKMG CMOS工艺制造,拥有高性能的可配置算术逻辑和数据通路电路,执行业界最常用的AES-128、AES-192、AES-256加密和解密标准的时候,性能最高可达惊人的53Gbps,而功耗只不过区区125mW。

Intel表示,这种芯片使用了近门槛值电压优化电路,具有非常宽的电压范围,最低320mV、最高1.1V,加密解密性能也可以据此灵活调整。

Intel还同时展示了一种全数字差异容限真随机数生成器,用于安全密钥生成,性能可达2.4Gbps。

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)