基于ARM-Linux的数据采集和网络传输系统设计

摘要:文中设计了一个基于ARM9处理器和嵌入式Linux OS的多路数据采集和网络传输系统。该系统以三星公司的S3C2440处理器为核心,配以DM9000百兆自适应网络控制芯片,通过互联网将由FPGA控制的多达64路AD采集通道采集的数据发送到网络终端上,实现了远程数据采集的功能。软件平台移植了最新的Linux 2.6.30.4内核,并基于Linux OS之上实现了Socket网络应用程序。随着互联网技术的不断发展,本系统在网络时代有着广阔的应用前景。

数据采集是实现工业现场控制的首要环节,实现远程数据传输是目前大多数工业控制系统的普遍要求。传统的数据采集方式是把各类基于ISA总线、PCI总线或USB总线的数据采集卡与计算机相连接,将传感器输出的信号经过信号调理电路的处理后,通过数据采集卡输入到计算机中。这种采集方式在不能安放计算机的场所进行将会非常困难,因此开发一套便携式的现场数据采集和网络传输系统具有十分重要的现实意义。本文基于ARM9嵌入式硬件平台和ARM—Linux OS,设计了这套数据采集和网络传输系统,可以对多达64路的模拟信号进行采集和处理,并将处理后的数据传送到远程网络终端上,同时满足多客户端请求的需要。

1 系统总体设计

本系统从功能上可分为两大子系统:数据采集子系统和网络传输子系统。其中数据采集系统有两个完全相同的模块,它们都连接在ARM处理器的系统总线上,如下图1所示。

1.1 数据采集子系统

该系统包含两个完全相同的采集板,板上的控制核心为Altera公司的cyclone II系列FPGA。每个采集板上有4片AD芯片MAX1308,由FPGA统一控制,而MAX1308是一款8通道AD芯片,所以该系统最多可同时实现64路独立通道的数据采集功能。单通道的数据吞吐率最高可达1075ks ps/通道,八通道的数据吞吐率最高可达456ksps/通道。两个采集板都挂在ARM的数据总线上,FPGA以异步FIFO存储机制与ARM数据总线进行交互。

1.2 网络传输子系统

该系统以ARM为控制核心,移植嵌入式Linux OS,网络芯片选用百兆自适应网卡DM9000EP,通过RJ-45接口接入互联网实现了数据的远程传输。基于TCP/IP协议实现了面向连接的数据流通信Socket网络应用程序,采用Linux服务器常用的C/S架构,完成了下位机的服务器程序和上位机的数据接收程序,并采用多进程编程思想解决了服务器多客户端问题。远程客户端通过配置服务器的IP地址和端口号,建立与服务器的连接后,即可请求数据,届时服务器启动数据采集系统并将采集的数据实时传送给远程客户端。

2 硬件设计

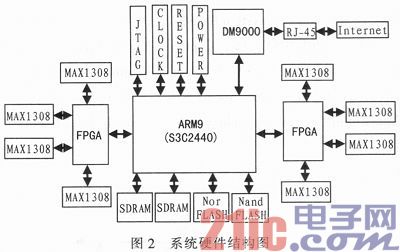

系统的硬件结构如下图2所示。以S3C2440芯片为核心,64 MB的SDRAM为系统内存,2 MB的NorFlash和512 MB的Nand Flash为系统存储设备。两片FPGA分别连接四片MAX1308芯片作为采集设备挂在S3C2440的系统总线上;DM9000网络芯片也挂在S3C2440的系统总线上,另一端通过隔离变压器H1102与RJ-45端口与互联网相连。

此外,系统时钟源直接采用外部晶振,内部PLL电路可以调整系统时钟,使系统运行速度更快。为了提供高效的电源监控作用,选取了专门的系统监视复位芯片MAX811S,实现对电源电压的监控和手动复位操作。该芯片优良,一旦系统电源低于系统复位的阈值(2.93V),复位芯片MAX811S将会对系统进行复位。S3C2440芯片内部有JTAG核,因此可以通过外部JTAG调试电缆与系统连接进行烧写u—boot。

2.1 AD采集电路

MAX1308是美信公司的一款12位8通道模数转换器,8个通道同时转换时,每个通道数据吞吐率为456ksps。独立的采样保持(T/H)电路为每个通道提供同时采样,提供输入范围,输入故障容限为,其他特性包括20 MHz T/H输入带宽、内部时钟、内部(+2.5 V)或外部(+2.0 V至+3.0 V)基准以及低功耗省电模式。20 MHz、12位双向并行数据总线用来提供转换结果,并可接受数字输入分别激活每一路通道。该器件

工作在+4.75 V至+5.25 V模拟电源与+2.7 V至+5.25 V数字电源下,全速运行时,总电源电流为57 mA。

![]() 为时钟模式选择输入,选择内部时钟时,将该引脚连接到AVDD;选择外部时钟时,将外部时钟连接到CLK,将该引脚连接到AGND。该系统选用内部信号,所以该引脚连接AVDD,并将CLK引脚连接到DGND。数字信号输出端D0~D11及启动转换输入CONVST、片选输入

为时钟模式选择输入,选择内部时钟时,将该引脚连接到AVDD;选择外部时钟时,将外部时钟连接到CLK,将该引脚连接到AGND。该系统选用内部信号,所以该引脚连接AVDD,并将CLK引脚连接到DGND。数字信号输出端D0~D11及启动转换输入CONVST、片选输入![]() 、写输入

、写输入![]() 、读输入

、读输入![]() 、转化结束输出

、转化结束输出![]() 、最后转换结束输出

、最后转换结束输出![]()

等引脚都接FPGA。

AD芯片MAX1308的电路图如图3所示。

2.2 CPU及FPGA硬件电路

该系统CPU为三星公司的S3C2440芯片,基于ARM920T内核,工作频率可达400 MHz,采用新的AMBA总线架构,是一款低电压、高性能的处理器芯片,片上集成众多的功能模块。S3C2440的存

ARM9 Linux 数据采集 网络传输 Socket 相关文章:

- 革新2410D开发板试用手记(04-21)

- 嵌入式Win CE中CAN总线控制器的驱动设计与实现(05-01)

- 嵌入式Web服务器移植与测试(03-03)

- 基于ARM9与Linux的门禁监控系统软件设计(03-08)

- 嵌入式Linux下基于ARM9的媒体播放的设计(03-27)

- SamsungS3C2440平台上的VxworksBSP移植(10-28)