Intel-镁光公布25nm NAND细节 采用Airgap技术

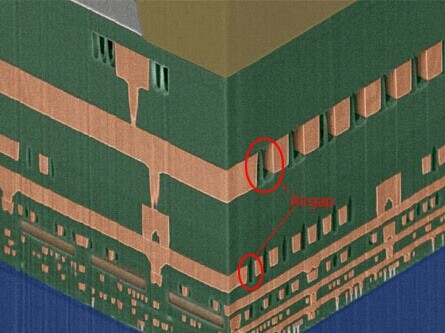

在本月6日至8日举办的IEDM2010旧金山大会上,Intel与镁光两家公司合作展示了其25nm NAND制程的细节,有趣的是,这种制程竟然会是首款将曾被IBM热捧的AirGap(空气隙型介电层)技术商用化的产品。

当初IBM用来解释Airgap的说明图

必须首先说明的是,Intel和镁光此前成立了一家NAND合资公司IM Flash,公司此前已经宣布正式将25nmNAND闪存芯片推出上市,不过此前双方都还没有透露这款芯片中使用了AirGap技术制作互联层的介电层。

Chipworks网站的分析师Dick James称:“这是首款商用化的应用了AirGap技术的产品。”包括IBM公司在内,许多公司都曾经热捧过这项技术,但该技术在他们的实际产品中均未开花结果。

在一份在IDEM上发布的文件中,Intel和镁光介绍了其64Gb密度的MLC NAND芯片产品,这款产品在芯片字线上的晶体管栅极半节距长度为24.5nm,位线方向上则为28.5nm,晶体管单元的面积为0.0028平方微米。文件中还称:“晶体管采用液浸式193nm光刻技术,配合了高级栅节距缩减技术,很好地控制了图形边缘的线性粗糙度和不同光刻对象关键尺寸的变化率。”

文件中还介绍称:“在25nm尺度,5%的关键长度变化率相当于3个晶格位置的长度.由于inhibit操作期间需要隔离6V左右的电压,因此晶体管功能区的浅槽隔离结构在深度方向上的尺寸很难明显缩减,这样产品的浅槽隔离结构的深宽比将高达7:1。而任何结构尺寸上的不一致,都会导致晶体管功能区的弯曲,举例而言,如果关键尺寸变化了3nm,那么沟道的错位距离可会高达10nm。因此,控制晶体管结构尺寸的稳定性,对保证NAND阵列的良好性能非常重要。过度缩减字线距离,会导致字线间电容的增加和晶体管界面电容的增加。”

文件最后部分写道:“要解决这个问题,我们引入了空气隙技术,这种结构将在字线之间生成;同时位线间我们也使用了这种技术。”

说明:Airgap技术即在介电层嵌入空气隙的技术,其本质与Low-K电介质的性质相同,均是试图减小导线间电容,提高电路运行速度的技术。

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)