STM32双核板的应用设计与ISP的从机软件升级

具备远程软件升级的设备具有更广泛的适用性,可以在设备安装到位后,通过软件升级在线修复一些问题,不但节省人力物力,也可以使设备的功能逐步完善。

双核板具有CAN总线,该总线不但是数据交换的通道,也是软件升级的通道。上位机可以通过CAN总线将需要升级的程序代码下传到A—CORE,A— CORE控制M—CORE的RST/ BOOT0引脚,使M—CORE复位并进入ISP状态,从而完成在线升级。由此可见,要实现基于CAN总线的在线软件升级,需要3个条件:一是待升级系统 M—CORE本身具有ISP功能,能通过串口实现程序的下载;二是A—CORE本身集成CAN总线,可通过CAN总线接收上位机发送的待升级程序代码;三是A-CORE可以控制M—CORE的RST/BOOT0引脚,完成在线升级。

3. 1 STM32的ISP升级

ISP(In-System Programming)方式相对于传统的并行编程方式有了极大的进步,无需将单片机从电路板上卸下就可进行编程。STM32系列芯片复位时,可以通过BOOT1和BOOT0的逻辑电平来决定系统的启动模式,见表1所列。

系统复位时,CPU根据这两个引脚的逻辑电平把相应模式的起始地址映射到启动空间(0x 0000 0000)。在启动延迟之后,CPU从位于0x0开始的启动存储区执行代码。由于实际应用中很少从内嵌SRAM中启动,故可将BOOT1引脚直接设置为低电平,只通过判断BOOT0引脚的高低电平来选择从用户闪存或系统存储器中启动。若复位时BOOT0的逻辑电平为高,则复位后从系统存储器启动,可通过 USART1与Bootloader进行通信。

STM32芯片具有开放式的在线烧录ISP协议,允许第三方根据该协议编写ISP下载软件,对STM32芯片进行FLASH的更新操作。在进行ISP方式升级时,先发送0x7F实现自动波特率匹配,能够识别最高115 200 bps的串口波特率。如果正确回应0x79,表示命令执行正常。握手正确后,就可以通过ISP命令实现对STM32的ISP操作,完成FLASH的擦除和编程。

3.2 FLASH分区存储

STM32F107片内集成256 KB FLASH和64 KBSRAM,FLASH由主存储块(Main Block)和信息块(Information Block)组成。主存储块用于存放用户程序,每页2 KB,共128页,容量为32K×64位,地址范围为0x0800 0000~0x 0803 FFFF;信息块容量为2 360×64位,分为启动程序代码和用户选择字节。启动程序代码从0x 1FFF B000~0x 1FFF F7FF,共18 KB,用户选择字节从0x 1FFF F800~0x 1FFF F80F,共16字节。

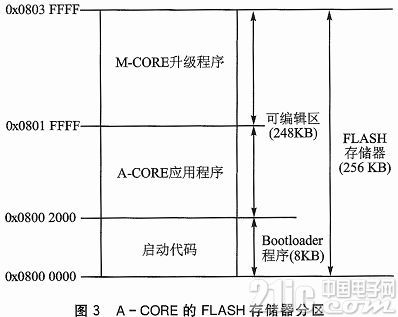

A-CORE的FLASH存储器分区如图3所示。

0x0800 0000~0x0800 1FFF,共8 KB空间,为Boot-loader代码空间。

0x0800 2000~0x0801 FFFF,为120 KB空间,存放A-CORE自身程序。

0x0802 0000~0x0803 FFFF,为128 KB空间,存放M-CORE应用程序。

上述空间分配,虽然升级程序的空间受到了限制,但在大多数情况下是可行的,因为A—CORE和M—CORE任务分担,其本身的程序量均不足总FLASH容量的一半。如果出现了空间不足的现象,完全可以换用更大容量的MCU。

3.3 软件升级流程

要完成A—CORE对M—CORE的软件升级,其过程可以分为两个阶段:基于CAN总线的数据传输和基于USART的ISP过程。

(1)基于CAN总线的数据传输

当M—CORE需要更新用户程序时,上位机将编译成功的M—CORE升级程序的HEX文件通过CAN总线发送到A—CORE。上位机先发送升级指令,A—CORE接收到升级指令后,将FLASH中M—CORE升级程序区(0x 0800 2000~0x 0801 FFFF)擦除,擦除成功后回复上位机,若回复错误信息,则退出升级;上位机接收到回复后,按行发送HEX文件内容,A—CORE接收到数据后,依次写入A—CORE的M—CORE升级程序区(0x 08002000~0x 0801 FFFF)中,接收完毕后向上位机发送写入完毕指令。

(2)基于USART的ISP过程

当A-CORE接收到上位机发送的升级执行指令后,升级流程如下:

①置M-CORE的BOOT0引脚为高电平,然后置RST引脚为低电平,复位M-CORE,使其从系统的内存模式启动,然后将RST引脚拉高。

②A—CORE向M—CORE发送0x7F,M—CORE接收该数据,并根据该数据与A—CORE自动匹配波特率,进行回复。若回复0X79,则表示可以进行相关擦除和写FLASH操作了,若回复0x1F,则升级失败。

③A—CORE收到正确的应答,则发送0x44+0xBB,根据程序大小擦除FLASH,根据STM32F107内部固有的Bootloader串口协议,擦除完成后回复A—CORE。

④A—CORE等待接收M—CORE的回复,收到正确的应答之后,发送0x31+0xCE,把存储到A—COREFLASH中的M—CORE升级程序区的内容写到M—CORE的相应FLASH中,一

- STM32学习笔记:在IAR中建立FWlib 3.0项目(08-13)

- 基于STM32单片机的火控系统信号采集测试(11-14)

- 基于LabVIEW的STM32调试平台设计(11-17)

- 基于STM32的LF RFID识别系统设计(11-25)

- STM32中断与嵌套NVIC快速入门(01-25)

- 基于TLC5947的旋转LED屏显示控制器设计(01-25)