基于1394b总线仿真设备的WDM驱动开发

方面,突发性大数据量传输发生率比较高,而windows环境下每个进程占用处理器的时间应小于50微秒,所以该驱动在PNP(Plug and Play)

为每个节点设置一个线程(PsCreateSvstemThread)对突发的大数据量数据进行平滑处理,以保证数据平稳的交由上层,该线程为事件驱动类型。并且通过KeCetCurrentThread和KeSetPriorityThread调整线程优先级。

当中断发生,中断处理函数记录中断状态并清除中断,判断中断是否为空,如果不为空则通过IoRequestDpc请求DPC,同时把相应的中断状态传给DPC。DPC通过中断状态判断中断类型和发生中断的节点,并且置位对应线程的线程事件。线程触发后,从阻塞态变为就绪态,当该进程得到处理器资源,调用数据处理函数处理数据。

DMA:Windows是多任务非实时的操作系统,而DMA可以有效的避免CPU的调度而节省时间,提高设备的实时性。系统要求DMA的使用率尽可能的减少并且尽可能的快捷。本设计使用硬件侧DMA,由FPGA逻辑实现,DMA控制由驱动控制。

驱动软件对DMA进行初始化,当中断服务程序被调用,驱动程序根据DPRAM的0、1区标志获取新数据存放区域,并从该区获取新数据的刷新标记。如有新数据,则服务程序申请DMA资源,获取到DMA资源后,锁定DMA资源并启动(DMA源地址、目的地址、数据搬运长度、控制命令)I/O端口到主存区的DMA。DMA完成后上报完整中断并释放DMA资源。当上层调用IRP_MJ_DEVICE_CONTROL对DPRAM进行写操作时,驱动程序判断用户该次操作的DPRAM的内存大小,如果在32K~2048K字节之间,则启动主存区到I/O端口的DMA,如果大于则分次启动DMA,如果小于32K字节则单拍或者多拍操作。操作流程与启动接收DMA相同,操作完成则上报中断。

循环队列:快捷性是硬件的特性之一,而应用层相对于硬件是及其缓慢的。并且由于PCI数据包封包的影响,其总线实际带宽只有133 Mbps/s,而本1394b设备支持S100Mbps

和S400Mbps两种传输速率。所以为避免设备长时间工作带来内存递增、内存泄漏以及突发大数据量给PCI总线通信超负荷运转造成数据丢失现象,驱动利用IoAllocateMdl申请一块3M的内存区,供硬件软件交互循环利用的循环队列用以保证传输的有可靠性,以及安全性。

当中断服务程序被调用时,驱动启动DMA或者读写寄存器操作把数据从指定DPRAM区搬运到主存区,更新新的数据指针并通过软中断方式通知上层软件。上层软件通过Deviee IoCo ntrol对设备进行控制,当应用层对驱动进行操作时,驱动根据写指针与读指针的差值提供可操作的内存块给上层软件。

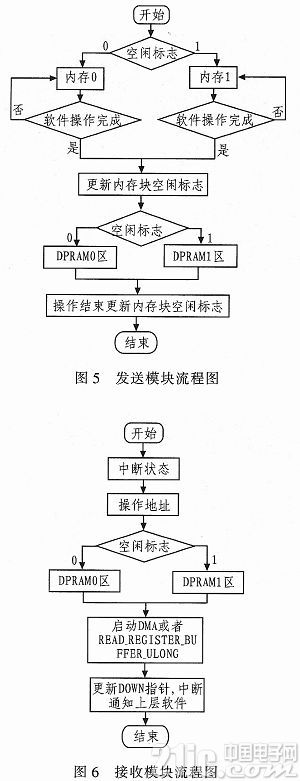

乒乓原理:乒乓原理不仅能够提高带宽的利用率,并且能够有效避免硬件与软件操作冲突情况的出现,并且避免了资源访问冲突的重试耗时,提高传输的有效性、实时性。驱动收发模块乒乓操作如图5和图6所示。

发送模块中,驱动软件与应用层交互,采用两块地址内存区。内存块操作由用户层软件操作,操作完成后切换内存区并通知驱动最新数据存放位置。驱动软件与硬件交互也采用两块DPRAM区。DPRAM的0、1区的切换操作由驱动软件进行操作,数据更新完毕的DPRAM交由逻辑处理并进行换区操作。

接收模块中,驱动软件设计循环队列与上层软件进行交互。硬件与驱动软件交互同样采用乒乓原理,该操作由硬件逻辑操作,驱动软件根据最新数据存放的DPRAM区,以及消

息新旧标记来进行数据处理。处理完成后完成数据新旧标志切换,并软中断方式通知应用层有新数据到达,应用层驱动返回的地址指针和内存大小获取最新数据。

3 验证分析

本设备提供DLL(Dynamic Link Library),采用Microsoft Visual Studio 2008专业版开发,封装为标准的动态链接库。提供Demo程序,图7为CC(Control computer)的发送数据窗口测试图,图8为RN(Remote Node)的接收数据的窗口测试图。

由上图可见驱动程序实现了1394b的S400 Mbps速率和PCI的S133 Mbps速率的跨速率通信数据不丢失,避免了软硬件交互产生的误码,使在S100 Mbps通信速率下平均带宽达到79.2 Mbps,在S400Mbps通信速率下平均带宽达到231.7 Mbps,实现了数据延时控制在us级别,实现了操作的准确性,保证了数据传输的确定性。

4 结束语

自2011年中国面临着国外大规模技术转移封锁以来,国内自研设备百花齐放,尤其是软件硬化无疑已经成为焦点。作为硬件灵魂的驱动程序越来越受到人们的重视。本文根据软硬件的特性进行软硬件工作协调,提高了硬件资源的利用率,提高了仿真通信的实时性,确定性,可靠性。由于需求要求该设备为PCI总线设备,通信的带宽受到限制,所以准备利用PCIe总线和实时操作系统提高设备的通信带宽

- 可编程图形芯片进入并行计算领域(06-06)

- Linux嵌入式系统开发平台选型探讨(11-09)

- CDMA2000基带信号发生器的FPGA+DSP实现(05-29)

- DSP中DMA操作的无阻塞请求实现(06-18)

- DSP嵌入式视频监测(06-02)

- 基于VxWorks的系统故障快速恢复设计(01-12)