CAN总线与以太网的嵌入式网关电路的设计与实现

本文从以太网与工业现场总线的互联出发,主要介绍了CAN总线与以太网嵌入式网关电路的设计与实现,本文对比了CAN 和以太网相连的嵌入式网关设计的两种方法,并从硬件结构和软件结构两方面进行了阐述。

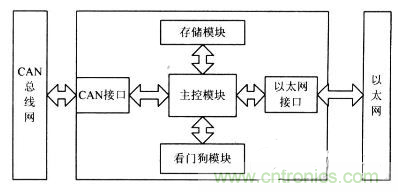

目前,对于CAN 和以太网相连的嵌入式网关设计主要有两种方法:一种是低档MCU 加接口芯片的设计方法,另一种是高档MCU 加EOS(实时多任务操作系统)再加接口芯片的设计方法。因CAN 只采用了ISO/OSI 参考模型的一、二层,协议相对简单,比较适合用于低成本、速率要求不高的离散控制系统。从合理的成本和有效利用处理能力这两方面考虑,该设计采用低档MCU 加接口芯片的方法,其硬件框图见图。

图1

主控芯片及以太网接口模块

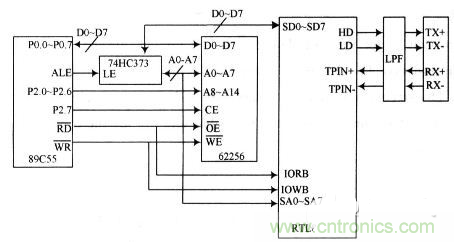

根据要求,该系统选择了性能价格比较高的AT89C55单片机。它是面向测控对象和嵌入式应用的,所以它的体系结构以及CPU、指令系统、外围单元电路都是按照这种要求专门设计的。它内部带高达20 KB 的FLASH程序存储器,AT89C55完全兼容8051 指令集,片上FLASH方便了使用者进行在线编程,工作速率最高可达33 MHz,256 B 的内部RAM,32 个可编程的I/O口,3 个16 位的定时/计数器,8 个中断源,支持低功耗的空闲工作模式。

以太网接口选用的是RTL8019AS 芯片,它是一种高度集成的以太网控制器,能实现以太网媒介访问层(MAC)和物理层(PHY)的全部功能。RTL8019AS 内部有两个RAM 区域:一是16 KB,地址为0x4000~0x7fff,要接收和发送数据包必须通过DMA 读写RTL8019AS 内部的16 KB 的RAM,它实际上是双端口RAM,即有两条总线与其连接,一条总线用于RTL8019AS读/写或写/读该RAM,即本地DMA;另一条总线用于单片机读或写该RAM,即远程DMA;二是32 个字节,地址为0x0000~0x001F,用于存储以太网物理地址。主控芯片和以太网接口芯片的硬件接口原理图见图2。值得注意的是由于以太网的包最大可以超过1 500 个字节,AT89C55的片内RAM 只有256 个字节,因此无法存储这么大的包,所以这里扩展了一个32 KB 的外部RAM,这样同时也能提高单片机的数据传输速度。

图2 以太网接口电路原理图

CAN 接口模块

组成CAN 系统的主要器件是CAN 控制器和收发器。该设计中,CAN 接口模块选用SJA1000 芯片和PCA82C250芯片。SJA1000 是一个独立的CAN 控制器,它是Philips 公司另一个CAN 控制器PCA82C200 的替代产品,且增加了一种新的工作模式(Peli CAN),这种模式支持CAN 2.0B 协议。SJA1000主要完成CAN 的通信协议,实现报文的装配和拆分、接收信息的过滤和校验等。PCA82C250是CAN 控制器与物理总线之间的接口,主要用于增强系统的驱动能力。采用收发器的系统中,节点数至少可以达到110 个,同时还具有降低射频干扰(RFI)和很强的抗电磁干扰(EMI)能力。

特别注意:

(1)晶振电路的问题。89C55 和SJA1000都应该有各自独立的晶振电路,不能够用SJA1000的时钟输出信号CLKOUT 来驱动单片机。

(2) 复位引脚的问题。虽然SJA1000的复位是低电平,但不能通过一个非门直接连接单片机的复位引脚。一般对解决复位引脚问题有两种方式:第一种是使用单片机的I/O 引脚控制SJA 的复位引脚,其好处是单片机可以完全控制SJA的复位过程;第二种是采用适当的复位芯片,为了降低成本,该设计采取的是第一种方法。

(3)RX1 引脚的电位必须维持在约0.5 VCC 上,否则将不能形成CAN 协议所要求的逻辑电平。

(4)一定要注意电缆的终端阻抗匹配,它直接影响CAN 总线是否能正常工作和网络性能。CAN 接口模块的硬件电路图见图3,在PCA82C250的RS 脚上接有一个斜率电阻R,可根据总线通信速度适当调整电阻的大小。

图3 CAN 接口模块的硬件电路图

- WindowsCE.Net下CAN卡的驱动程序设计(04-12)

- 对TTCAN的分析(05-26)

- 嵌入式Win CE中CAN总线控制器的驱动设计与实现(05-01)

- μC/OS-II的多任务信息流与CAN总线驱动(07-11)

- 采用CAN总线实现DSP芯片程序的受控加载(11-08)

- 基于DSP的电动汽车CAN总线通讯技术设计(10-08)