S3C2440的SDRAM驱动

刷新操作与预充电中重写的操作一样,都是用S-AMP先读再写。但为什么有预充电操作还要进行刷新呢?因为预充电是对一个或所有L-Bank中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些很长时间没经历重写的存储体中的数据。但与所有L-Bank预充电不同的是,这里的行是指所有L-Bank中地址相同的行,而预充电中各L-Bank中的工作行地址并不是一定是相同的。那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。这样刷新时间间隔就是:64m/行数s。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个L-Bank的行数。刷新命令一次对一行有效,刷新间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。刷新操作分为两种:Auto Refresh,简称AR与Self Refresh,简称SR。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。对于AR,SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS在RAS之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

SDRAM相关寄存器:

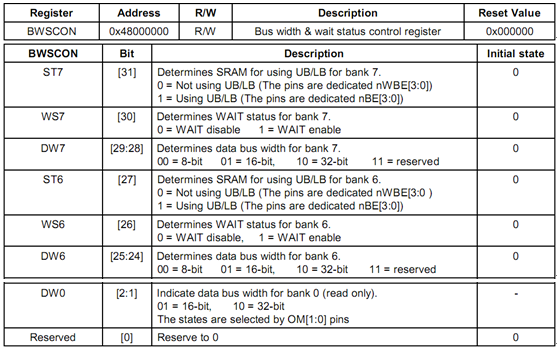

(1)BWSCON寄存器(BUS WIDTH & WAIT CONTROL REGISTER)

表2-17 SDRAM控制寄存器(BWSCON)

根据开发板的存储器配置和芯片型号,设置每个BANK焊接芯片的位宽和等待状态

BWSCON,每4位对应一个BANK,这4位分别表示:

lSTx:启动/禁止SDRAM的数据掩码引脚(UB/LB),SDRAM没有高低位掩码引脚,此位为0,SRAM连接有UB/LB管脚,设置为1

注:UB/LB数据掩码引脚用来控制芯片读取/写入的高字节和低字节(对比硬件手册SDRAM和SRAM的接线图)

lWSx:是否使用存储器的WAIT信号,通常设为0

lDWx:设置焊接存储器芯片的位宽,笔者开发板使用两片容量为32M,位宽为16的SDRAM组成64M,32位存储器,因此DW7,DW6位设置为0b10,其它BANK不用设置采用默认值即可。

lBANK0对应的是系统引导BANK,这4位比较特殊,它的设置是由硬件跳线决定的,因此不用设置

lBWSCON设置结果:0x22000000

(2)BANKCON0~BANKCON5 (BANK CONTROL REGISTER)

表2-18 BANKCON0~BANKCON5控制寄存器(BANKCON0~BANKCON5)

这6个寄存器用来设置对应BANK0~BANK5的访问时序,采用默认值0x700即可

(3)BANKCON6~BANKCON7 (BANK CONTROL REGISTER)

表2-19 BANKCON6~BANKCON7控制寄存器(BANKCON6~BANKCON7)

由于内存都焊接在这两个BANK上,因此内存驱动主要是对这两个寄存器进行设置

lMT:设置BANK6~BANK7的存储器类型,

00=ROM or SRAM 01=保留

10=保留11=SDRAM

内存为SDRAM,设置为0b11,对应的应该设置Trcd和SCAN位,其它位和SDRAM无关

lTrcd:RAS to CAS Delay行地址选通到列地址选通延迟,这个参数请看后面的内存工作原理扩展部分解释,笔者内存芯片为HY57V561620,由其芯片手册可知其Trcd为最少20ns,如果内存工作在100MHz,则该值至少要为2个时钟周期,通常设置为3个时钟周期,因此设置为0b01

lSCAN:SDRAM Column Address Number SDRAM的列地址数,笔者内存芯片为HY57V561620,列地址数为9,设置为0b01

lBANK6,BANK7设置结果为:0x18005

(4)REFRESH (REFRESH CONTROL REGISTER)

表2-20刷新频率设置寄存器(REFRESH)

SDRAM的刷新有效,刷新频率设置寄存器(刷新)

lREFEN:开

S3C2440SDRAM驱 相关文章:

- S3C2440的SDRAM驱动 (11-10)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)