SDRAM工作原理及S3C2410 SDRAM控制器配置方法

据线上给出,以后每个时钟节拍给出一个新的数据,输入缓冲在猝发数据量满足要求后停止接受数据。猝发写操作可以被猝发读/写命令或DQM数据输入屏蔽命令和预充电命令或猝发停止命令中止。

6、自动刷新

由于动态存储器存储单元存在漏电现象,为了保持每个存储单元数据的正确性,HY57V561620必须保证在64ms内对所有的存储单元刷新一遍。一个自动刷新周期只能刷新存储单元的一个行,每次刷新操作后内部刷新地址计数器自动加“1”。只有在所有体都空闲(因为4个体的对应行同时刷新)并且未处于低功耗模式时才能启动自动刷新操作,刷新操作执行期间只能输入空操作,刷新操作执行完毕后所有体都进入空闲状态。该器件可以每间隔7.8μs执行一次自动刷新命令,也可以在64ms内的某个时间段对所有单元集中刷新一遍。

7、自刷新

自刷新是动态存储器的另一种刷新方式,通常用于在低功耗模式下保持SDRAM的数据。在自刷新方式下,SDRAM禁止所有的内部时钟和输入缓冲(CKE除外)。为了降低功耗,刷新地址和刷新时间全部由器件内部产生。一旦进入自刷新方式只有通过CKE变低才能激活,其他的任何输入都将不起作用。给出退出自刷新方式命令后必须保持一定节拍的空操作输入,以保证器件完成从自刷新方式的退出。如果在正常工作期间采用集中式自动刷新方式,则在退出自刷新模式后必须进行一遍(对于HY57V561620来说,8192个)集中的自动刷新操作。

8、时钟和时钟屏蔽

时钟信号是所有操作的同步信号,上升沿有效。时钟屏蔽信号CKE决定是否把时钟输入施加到内部电路。在读写操作期间,CKE变低后的下一个节拍冻结输出状态和猝发地址,直到CKE变高为止。在所有的体都处于空闲状态时,CKE变低后的下一个节拍SDRAM进入低功耗模式并一直保持到CKE变高为止。

9、DQM操作

DQM用于屏蔽输入输出操作,对于输出相当于开门信号,对于输入禁止把总线上的数据写入存储单元。对读操作DQM延迟2个时钟周期开始起作用,对写操作则是当拍有效。

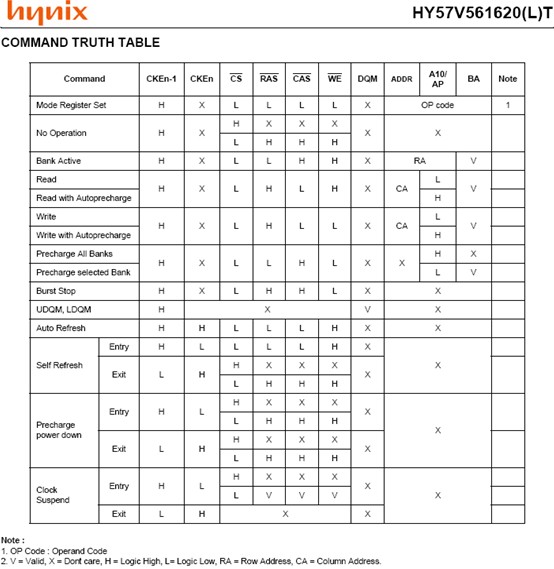

HY57V561620命令表如下图所示:

二、HY57V561620 SDRAM介绍

1、HY57V561620的结构

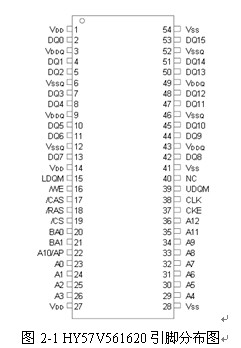

HY57V561620存储容量为4M×4bank×16位(32M字节),工作电压为3.3V,常见封装为54脚TSOP,兼容LVTTL接口,支持自动刷新(Auto-Refresh)和自刷新(Self-Refresh),16位数据宽度。

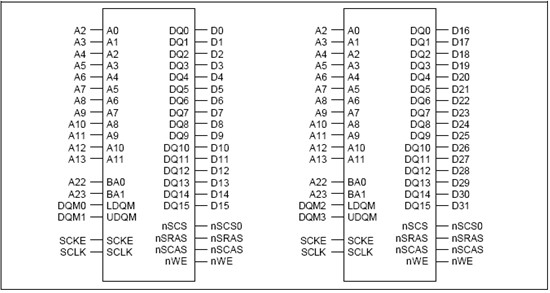

HY57V561620引脚分布如图2-1所示。

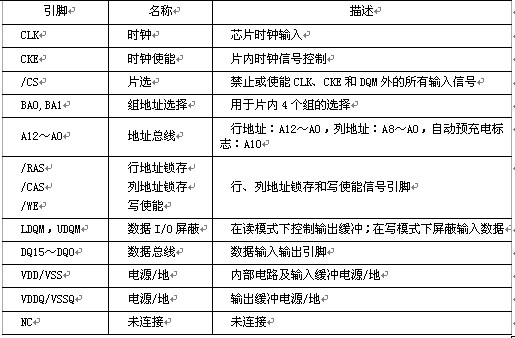

HY57V561620引脚信号描述

更具体的内容可参考HY57V561620的用户手册。

三、S3C2410和HY57V561620的接线方法

华清远见教学用的S3C2410开发板上使用的SDRAM的型号是HY57561620。规格是:

4Banks*4M*16Bit。采用两片SDRAM组成32位64M的内存空间。

1、确定BA0、BA1的接线

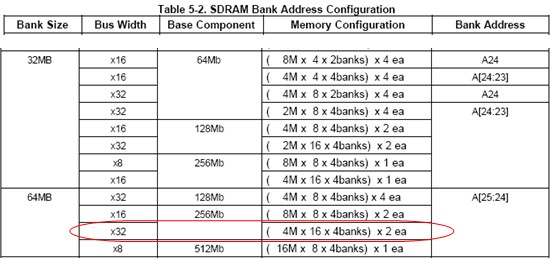

在S3C2410的Table 5-2. SDRAM Bank Address Configuration给出了SDRAM接线的参考方法。

上表中各段含义及和我们平台的对应:

Bank Size: 每个Bank的大小 (HY57561620是4M*16=64MB)Bus Width: 总线宽度 (两颗HY57561620,32位)

Base Component:个体容量 (256Mb)

Memory Configration:内存配置 ((4M*16*4banks)*2ea )

所以Bank Address对应A[25:24],此处确定了HY57561620的BA0和BA1和S3C2410之间的接线。

2、确定其它接线

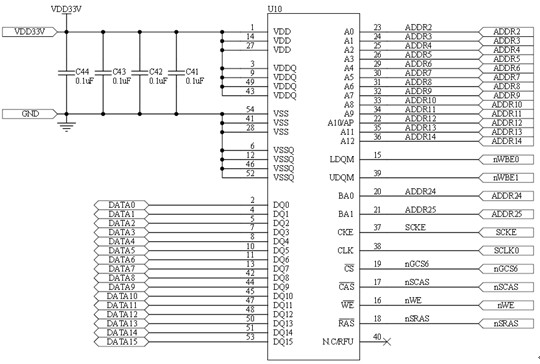

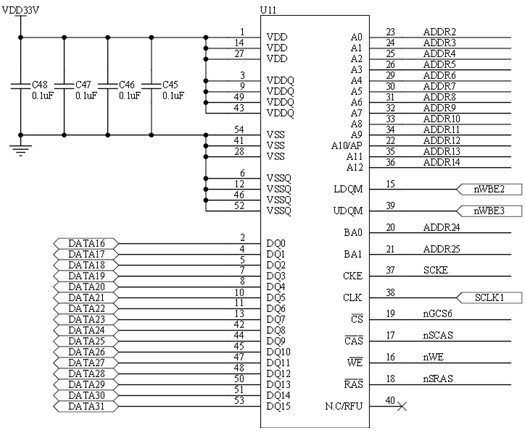

上图是S3C2410手册中给出的参考接线,通过这个图可以确定HY57561620和S3C2410之间除BA0、BA1的所有其它接线。本例中,详细的接线方法如“接线原理图”小节。

3、接线原理图

引脚描述如下:

nSRAS:SDRAM行地址选通信号

nSCAS:SDRAM列地址选通信号

nGCS6:SDRAM芯片选择信号(选用Bank6作为sdram空间,也可以选择Bank7)

nWBE[3:0]:SDRAM数据屏蔽信号

SCLK0[1]:SDRAM时钟信号

SCKE:SDRAM时钟允许信号

DATA[0:31]:32位数据信号

ADDR[2:14]:行列地址信号

ADDR[25:24]:bank选择线

四、S3C2410 SDRAM控制器的配置方法

在系统使用SDRAM之前,需要对S3C2410X的存储器控制器进行初始化。其中对与SDRAM(Bank6)相关的寄存器进行了特殊的设置,以使SDRAM能够正常工作。由于C语言程序使用的数据空间和堆栈空间都定位在SDRAM上,因此,如果没有对SDRAM(Bank6)的正确初始化,系统就无法正确启动。下面介绍与SDRAM相关的寄存器设置。

1、BWSCON寄存器

BWSCON寄存器主要用来设置外接存储器的总线宽度和等待状态。在BWSCON中,除了Bank0,其他7个bank都各对应4个相关位的设置,分别为STn,WSn和DWn。这里只需要对DWn进行设置,例如SDRAM(Bank6)采用32位总线宽度,因此,DW6=10,其他2位采用缺省值。BWSCON寄存器在Bank6上的位定义如表4-1所示。

表4-1 BWSCON寄存器在Bank6上的位定义

BWSCON | 位 | 描述 |

SDRAMS3C2410控制器配 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)