51手记之C8051F

口是一个双线的双向串行总线。与I2C串行总线兼容。在作为主或从器件时,数据传输的最大速率可达系统时钟频率的十分之一(这可能比SMBus的规定速度要快,取决于所使用的系统时钟)。可以采用延长低电平时间的方法协调同一总线上不同速度的器件。。SMBus提供了SDA(串行数据)控制、SCL(串行时钟)产生和同步、仲裁逻辑以及起始/停止的控制和产生电路。

SCL(串行时钟)和SDA(串行数据)线是双向的,必须通过一个上拉电阻或等效电路将它们连到电源电压。连接在总线上的每个器件的SCL和SDA都必须是漏极开路或集电极开路的,因此当总线空闲时,这两条线都被拉到高电平。总线上的最大器件数只受规定的上升和下降时间的限制,上升和下降时间分别不能超过300ns和1000ns。

所有的数据传输都由主器件启动,可以寻址一个或多个目标从器件。主器件产生一个起始条件,然后发送地址和方向位。

一个主器件只能在总线空闲时启动一次传输。在一个停止条件之后或SCL和SDA保持高电平已经超过了指定时间,则总线是空闲的。两个或多个主器件可能在同一时刻启动数据传输,所以使用仲裁机制迫使一个主器件放弃总线。试图发送高电平的主器件将检测到SDA上的低电平而退出竞争。赢得总线的器件继续其数据传输过程,而未赢得总线的器件成为从器件并在后续的传输中接收数据(如果被寻址)。

每次数据字节或从地址传输都产生SMBus中断。发送数据时在ACK周期后产生中断,使软件能读取接收到的ACK值;接收数据时在ACK周期之前产生中断,使软件能确定要发出的ACK值。

SMBus接口可以被配置为工作在主方式和/或从方式。在任一时刻,它将工作在下述4种方式之一:主发送器、主接收器、从发送器或从接收器。

9.可编程计数器阵列(PCA0)

提供增强的定时器功能,与标准8051的计数器/定时器相比,它需要较少的CPU干预。PCA由一个专用的16位计数器/定时器和5个16位捕捉/比较模块组成。每个捕捉/比较模块有其自己的I/O线(CEXn),这些I/O线在被允许时通过交叉开关连到端口I/O。

定时器的时基信号可以在六个时钟源中选择:系统时钟、系统时钟/4、系统时钟/12、外部振荡器时钟/8、定时器0溢出或ECI输入引脚上的外部时钟信号。

PCA的模块4可被用作看门狗定时器(WDT),在系统复位后即被使能为该方式。在看门狗方式被使能时,对某些寄存器的访问受到限制

1)PCA计数器/定时器

16位的PCA计数器/定时器由两个8位的SFR组成:PCA0L和PCA0H。在读PCA0L时,“瞬象寄存器”自动锁存PCA0H的值,随后读PCA0H时将访问这个“瞬象寄存器”;先读PCA0L寄存器可以保证正确读取整个16位PCA计数器的值。

当计数器/定时器溢出时(从0xFFFF到0x0000),PCA0MD中的计数器溢出标志(CF)被置为逻辑‘1’并产生一个中断请求

2)捕捉/比较模块

每个模块都可被配置为独立工作,有六种工作方式:边沿触发捕捉、软件定时器、高速输出、频率输出、8位脉宽调制器和16位脉宽调制器。

a.边沿触发的捕捉方式

CEXn输入信号必须在高电平或低电平期间至少保持两个系统时钟周期,以保证能够被硬件识别。

b.软件定时器方式

在该方式,PCA将计数器/定时器的计数值与模块的16位捕捉/比较寄存器(PCA0CPHn和PCA0CPLn)进行比较。当发生匹配时,PCA0CN中的捕捉/比较标志(CCFn)被置为逻辑‘1’并产生一个中断请求;当向PCA0的捕捉/比较寄存器写入一个16位数值时,应先写低字节。

c.高速输出方式

每当PCA计数器与模块的16位捕捉/比较寄存器(PCA0CPHn和PCA0CPLn)发生匹配时,模块的CEXn引脚上的逻辑电平将发生变化。当向PCA0的捕捉/比较寄存器写入一个16位数值时,应先写低字节。

d.频率输出方式

可在模块的CEXn引脚产生可编程频率的方波。。捕捉/比较模块的低字节与PCA0计数器的低字节比较;两者匹配时,CEXn的电平发生改变,方波频率=Fpca/(2*PCA0CPHn),PCA0CPHn中的值为0x00时,相当于256。

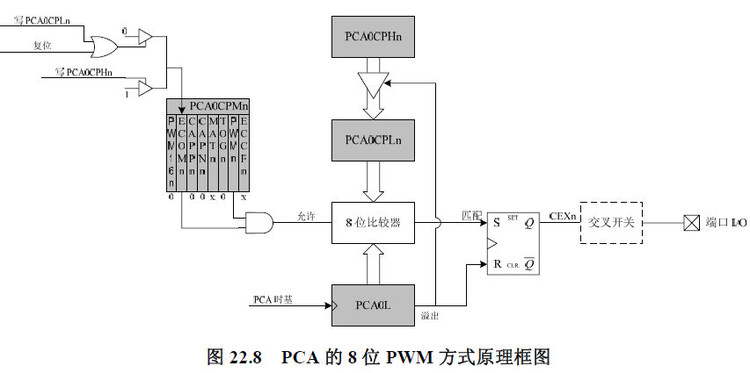

e.8位脉宽调制器方式

PWM输出的频率取决于PCA计数器/定时器的时基。使用模块的捕捉/比较寄存器PCA0CPLn改变PWM输出信号的占空比。当PCA计数器/定时器的低字节(PCA0L)与PCA0CPLn中的值相等时,CEXn引脚上的输出被置‘1’;当PCA0L中的计数值溢出时,CEXn输出被复位

占空比=(256-PCA0CPHn)/256

f.16位脉宽调制器方式

当PCA计数器与模块的值匹配时,CEXn的输出被置为高电平;当计数器溢出时,CEXn输出被置为低电平。为了输出一个占空比可变的波形,新值的写入应与PCA的CCFn匹配中断同步。

占空比=(65536-PCA0CPn)

51手记C8051 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)