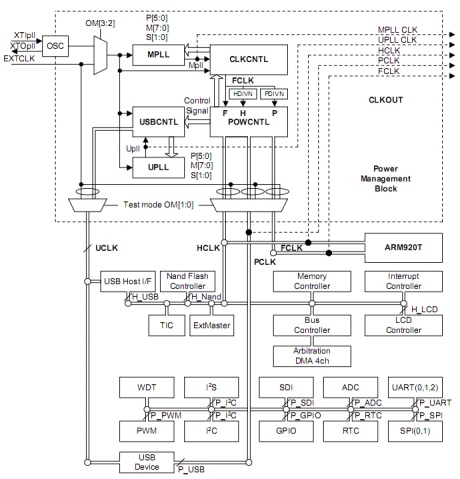

S3C2410时钟&电源管理单元

The clock & power management block consists of three parts:clock control, USB clk control, and power control.

Clock control logic

The Clock control logic in S3C2410X can generate the required clock signals includingFCLK for CPU, HCLK for

the AHB bus peripherals, and PCLK for the APB bus peripherals.

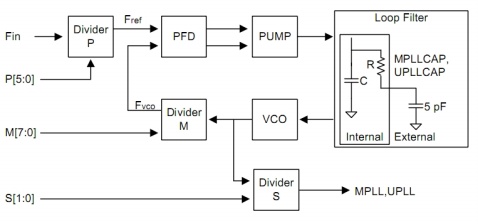

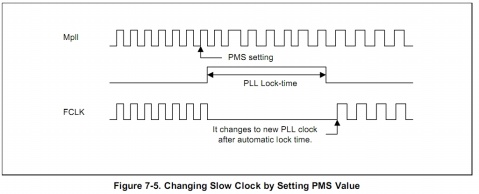

The S3C2410X has two Phase Locked Loops

(PLLs):on

can make slow clocks without PLL and connect/disconnect the clock to each peripheral block by software, which

will reduce the power consumption.

The main clock source comes from an external

crystal (XTIpll) or an external clock (EXTCLK). The clock generator includes an oscillator (Oscillation Amplifier),

which is connected to an external crystal, and also has two PLLs (Phase-Locked-Loop), which generate the high

frequency clock required in the S3C2410X.

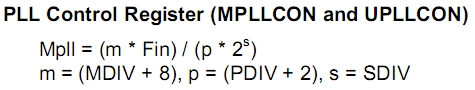

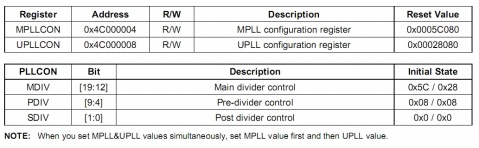

MPLL锁相环模块(提供FLCK/HCLK(AHB)/PCLK(APB)) UPLL锁相环模块(提供UCLK)相同

S3C2410时钟电源管理单 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)