MCS-51的中断系统

能够实现中断处理功能的部件称为中断系统;产生中断的请求源称为中断请求源。

中断源向CPU提出的处理请求,称为中断请求(或中断申请)。

进入中断→保护现场→中断处理恢复现场→中断返回

中断方式优点:大大地提高了CPU的工作效率。

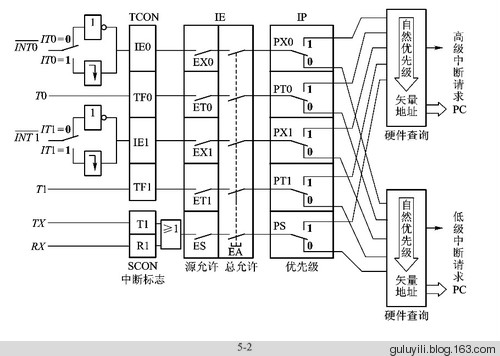

5.3 中断请求源 五个中断请求源 : (1)INT0*—外部中断请求0,由引脚INT0*输入,中断请求标志为IE0。 (2)INT1*—外部中断请求1,由引脚INT1*输入,中断请求标志为IE1。 (3)定时器/计数器T0溢出中断请求,中断请求标志为TF0。 (4)定时器/计数器T1溢出中断请求,中断请求标志为TF1。 (5)串行口中断请求,中断请求标志为TI或RI。 由特殊功能寄存器TCON和SCON的相应位锁存。

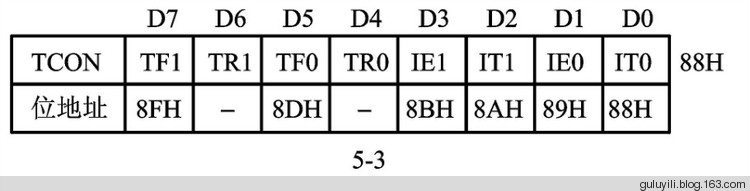

包含:

(1)T0和T1的溢出中断请求标志位TF1和TF0

(2)外部中断请求标志位IE1与IE0。格式如下所示:

各标志位的功能:

(1)IT0—选择外部中断请求0为跳沿触发方式还是电平触发方式:

IE0=1,外部中断0有中断请求。当CPU响应该中断,转向中断服务程序时,由硬件清“0”IE0。

(3)IT1—外部中断请求1为跳沿触发方式还是电平触发方式,意义与IT0类似。

(4)IE1—外部中断请求1的中断请求标志位,意义与IE0类似。

T0计数后,溢出时,由硬件置“1”TF0,向CPU申请中断,CPU响应TF0中断时,硬件自动清“0”TF0,TF0也可由软件清0。

当MCS-51复位后,TCON被清0,则CPU关中断,所有中断请求被禁止。

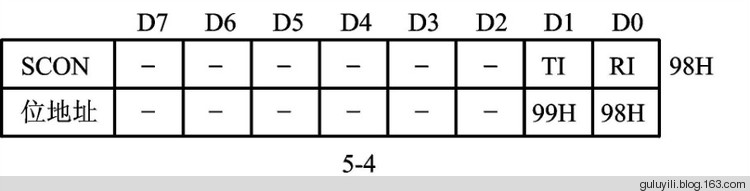

SCON为串行口控制寄存器,字节地址为98H。串行口的发送中断和接收中断的中断请求标志TI和RI,格式如下:

各标志位的功能:

(1)TI—发送中断请求标志位。串口每发送完一帧串行数据后,硬件自动置“1”TI。必须在中断服务程序中用软件对TI标志清“0”。

2)RI—接收中断请求标志位。串口接收完一个数据帧,硬件自动置“1”RI标志。必须在中断服务程序中用软件对RI标志清“0”。

5.4 中断控制

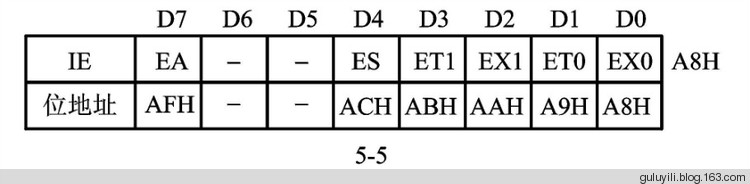

5.4.1 中断允许寄存器IE

CPU对中断源的开放或屏蔽,由片内的中断允许寄存器IE控制。字节地址为A8H,可位寻址。格式如下:

总的开关中断控制位EA(IE.7位):

EA=0,所有中断请求被屏蔽。

EA=1,CPU开放中断,但五个中断源的中断请求是否允许,还要由IE中的5个中断请求允许控制位决定。

1:CPU开放所有中断(CPU开中断)。

1:允许串行口中断。

MCS-51复位后,IE清0,所有中断请求被禁止。 若使某一个中断源被允许中断,除了IE相应的位的被置“1”,还必须使EA位=1。

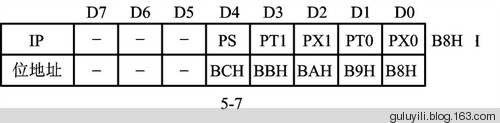

IP各个位的含义:

(1)PS——串行口中断优先级控制位

0:低优先级中断。

MCS-51中断系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)