Msp430时钟设计与寄存器说明

4.1基础时钟模块+介绍

基础时钟模块+支持低系统消耗和超低功耗。采用三种片内时钟信号,用户可以选择合适

的性能和低功耗。基础时钟模块只需接一个外部电阻、一个或两个外部晶体、或者用振荡器,

通过软件控制。

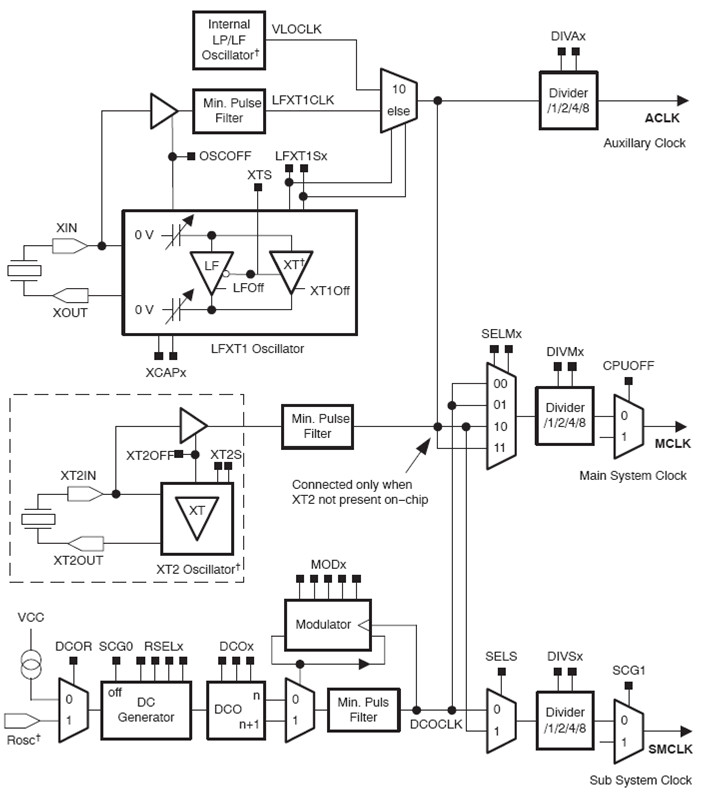

基础时钟模块+有4个时钟源:

LFXT1CLK:由低频时钟晶体或外接32768Hz时钟源产生的低频/高频振荡器或由标准晶

体、振荡器,或外部400KHz~16MHz的外部时钟源提供。

XT2CLK:可供选择的高频振荡器,由标准晶体、振荡器,或外部400KHz~16MHz的外

部时钟源提供。

DCOCLK:片内可数字控制的振荡器。

VLOCLK:片内超低功耗、12KHz的低频振荡器。

基础时钟模块可提供的三种时钟信号:

ACLK:辅助时钟。ACLK由软件选择来自LFXT1CLK和VLOCLK之一的时钟信号。ACLK

经1,2,4,8分频后得到。ACLK可由软件选作各个外围模块。

MCLK:主时钟。MCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(如果片内提

供),DCOCLK之一的时钟信号。MCLK由1,2,4,8分频得到。MCLK用于CPU和系统。

SMCLK:子系统时钟。SMCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(片内

提供),DCOCLK之一的时钟信号。SMCLK由1,2,4,8分频得到。SMCLK可由软件选作

各个外围模块。

基础时钟模块的方框图如图所示。

注:个别特殊的时钟并不是所有的MSP430x2xx系列器件都具有一样的时钟特性。如

MSP430x20xx:LFXT1不支持高频模式,没有XT2,不支持晶体振荡器。MSP430x21xx:

没有内部低功耗/低频振荡器,没有XT2,不支持晶体振荡器。MSP430x22xx:没有XT2。

4.1基础时钟模块+寄存器

基础始终模块+的寄存器列于表中。

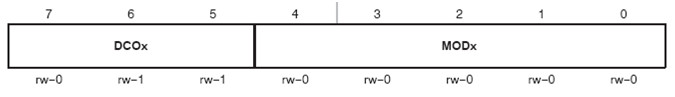

DCO控制寄存器-DCOCTL

DCOX位DCO频率选择。这几位选择由RSELX设置定义的八个7-5离散频率中的一个。

MODX位调节器选择。这几位决定在32个DCOCLK周期内

4-0 fDCO+1频率被用的次数。在持续的时钟周期以内(32-MOD)fDCO频率被采用。

当DCOX=7时不被采用。

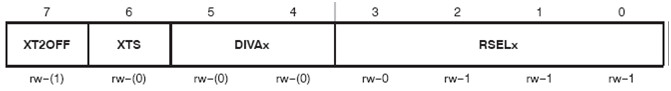

基础时钟系统控制寄存器1—BCSCTL1

XT2OFF7位关闭XT2。该位关闭XT2振荡器

0 XT2打开

1 XT2不用于SMCLK或MCLK则关闭

XTS6位LFXT1模式选择

0低频率模式

1高频率模式

divAX5-4位ACLK分频

00 /1

01 /2

10 /4

11 /8

RSELX3-0位范围选择。十六种频率范围可供选择。通过设置RSELX=0

来选择最低频率。当DCOR=1时,RSEL3无效。

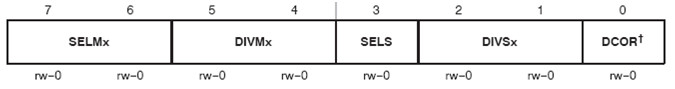

基础时钟系统控制寄存器2—BCSCTL2

注"+"的不使用于MSP430X20XX或MSP430X21XX系列器件

SELMX7-6位选择SMCLK。这两位选择MCLK的时钟源

00 DCOCLK

01 DCOCLK

10当XT2振荡器在片内时采用XT2CLK。当XT2振荡器不在

片内时采用LFXT1CLK或VLOCLK

11 LFXT1CLK或VLOCLK

divMX5-4位MCLK分频

00 /1

01 /2

10 /4

11 /8

SELS3位选择SMCLK。该位选择SMCLK的时钟源

0 DCOCLK

1当XT2振荡器存在时选用XT2CLK,当XT2振荡器不存在

时采用LFXT1CLK或VLOCLK

divSX2-1位SMCLK分频

00 /1

01 /2

10 /4

11 /8

DCOR0位DCO寄存器选择

0内部寄存器

1外部寄存器

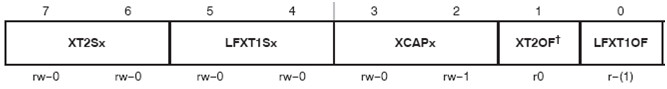

基础时钟系统控制寄存器3—BCSCTL3

注"+"的不使用于MSP430X2XX,MSP430X21XX或MSP430X22XX系列器件。

XT2SX7-6位XT2范围选择。这些位选择XT2的频率范围。

00 0.4-1MHz晶体或振荡器

01 1-3MHz晶体或振荡器

10 3-16MHz晶体或振荡器

11 0.4-16MHz外部数字时钟源

LFXT1SX5-4位低频时钟选择和LFXT1范围选择。当XTS=0时在LFXT1和VLO

之间选择。当XTS=1时选择LFXT1的频率范围。

当XTS=0时:

00 LFXT1上的32768Hz晶体

01保留

10 VLOCLK(MSP430X21X1器件上保留)

11外部数字时钟信源

XCAPX3-2位振荡器电容选择。这些位选择当XTS=0时用于LFXT1的有效电容。

00 1Pf

01 6 Pf

10 10 Pf

11 12.5 Pf

XT2OF1位XT2振荡器失效

0不存在失效条件

1存在失效条件

LFXT1OF0位LFXT1振荡器失效

不存在失效条件

存在失效条件

应用源程序的部分代码:

BCSCTL1= CALBC1_1MHZ;//关闭振动器 内部最高 定义内部时钟频率 1、8、12、16

DCOCTL|= CALDCO_1MHZ; //定义最高频率 在31次中两种频率

BCSCTL2|=0x30+SELM0;

BCSCTL1&=~XT2OFF;

BCSCTL3|=XCAP1;

Msp430时钟设计寄存器说 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)