LPC1114通用输入/输出端口(GPIO)续

IO引脚上有中断请求。该寄存器也只用了32位中的低12位,当位为0 时表明对应引脚上没有外部中断请求发生,为1时表明对应引脚上有外部中断请求发生,12位与12个引脚一一对应,每位设置对应一个引脚。在复位时RIS的值为全0,表明所有的引脚复位时都没有外部中断请求发生。如果某个引脚上RIS对应的值为1,则表明该引脚上有符合条件的中断请求发生,此时若对应的IE位也为1(即开启该引脚的中断功能),就会发生该引脚的中断响应。但如果对应的IE位不为1,则不会响应中断。

接下来是MIS寄存器,其偏移地址为0x8018,属性为只读,它和上面的RIS寄存器基本是一样的,可以用于查询是否有中断响应。不同点在于,RIS是只要引脚上满足中断触发条件它对应的位就被置1,但它不一定被响应,因为它有可能被屏蔽了(例如对应的IE位没有被置1),因此RIS不能判定中断是否响应了,而只能判定有符合条件的中断请求发生;但在MIS寄存器中,若相应的位被置1了,则说明这个中断一定被响应了,因此可以通过程序查询MIS寄存器的方式来判断是否有中断被响应,是哪个引脚上的中断被响应。其实MIS寄存器表征的就是屏蔽之后的中断状态,它也只用了32位中的低12位,当位为0 时表明对应引脚上没有外部中断响应,为1时表明对应引脚上有外部中断响应,12位与12个引脚一一对应,每位设置对应一个引脚。

最后一个是IC寄存器,其偏移地址为0x801C,属性为只写,它用来清除中断边沿检测逻辑。它也只用了32位中的低12位,当位为0 时不起作用,即对外部中断无任何影响,为1时表明对应引脚上的边沿触发端口位被清零,12位与12个引脚一一对应,每位设置对应一个引脚。之所以要设IC寄存器,是因为在中断响应后(仅边沿型触发),在RIS和MIS寄存器中相应的位不会被自动清零,因此在中断响应后需要在IC寄存器的相应位中写1来进行清零,以保证后续中断的正常触发。

以上是GPIO中各寄存器功能的基本介绍,至于详细的使用方法,会在后面中断一章中做详细讨论,这里先不赘述了。

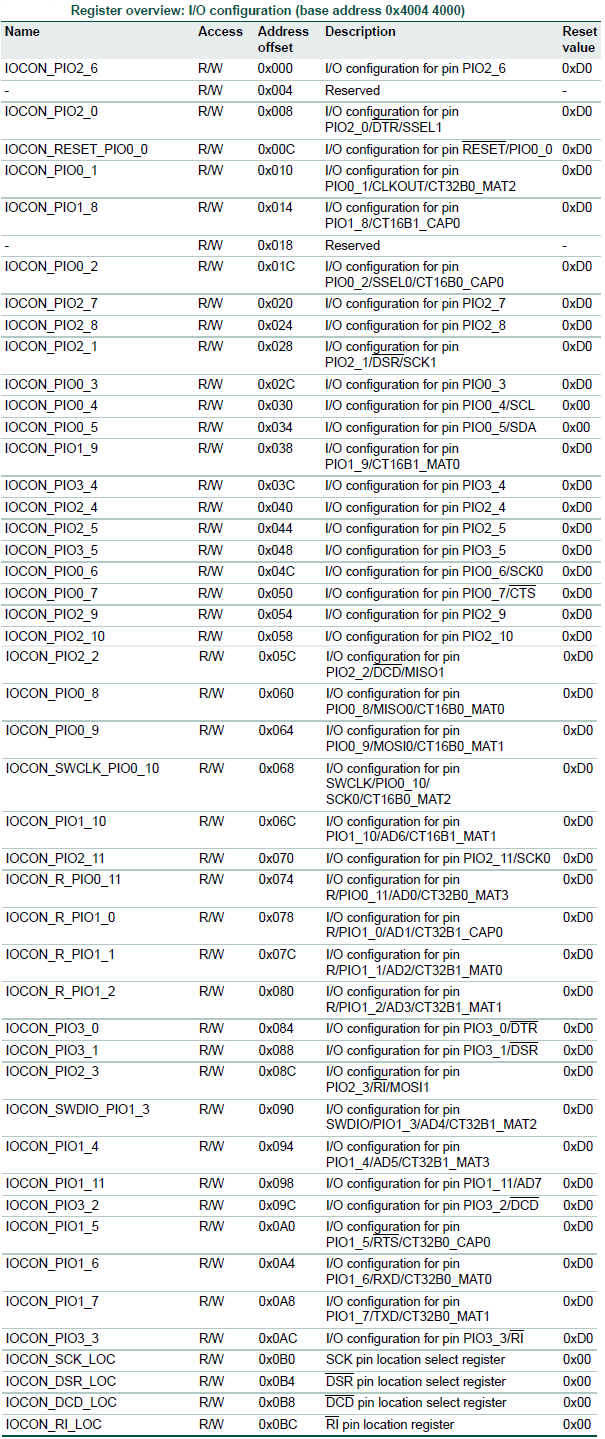

接下来讨论一下GPIO端口引脚的配置。从第一章中已经知道,LPC1114引脚复用的很多,除了第0端口中的3、第2端口中的2~10和第3端口中的4、5引脚外,其余的引脚都具有第二功能。甚至包括复位端RESET都复用在了GPIO0_0引脚。为了实现引脚上各复用功能间的切换,在处理器内部专门设立了一个引脚配置寄存器IOCON。用户可以通过IOCON来配置每一个I/O的下列功能特性:

引脚复用功能;

内部上拉/下拉电阻或总线保持功能;

滞后模式;

引脚控制ADC输入的模拟模式或数字模式;

引脚控制I2C功能的I2C模式。

每个引脚对应一个IOCON寄存,所以对于LPC1114来说,至少应该有42个IOCON寄存器(其实共有46个,多出的4个用于其它功能设置)。一般来说,在使用任何引脚之前都应该先配置一下它所对应的IOCON寄存器,除非用的是引脚的默认功能。下面给出LPC1114中所有引脚的IOCON寄存器情况,如下表。

typedef struct

{

__IO uint32_t PIO2_6; /*!< Offset: 0x000 (R/W) I/O configuration for pin PIO2_6 */

uint32_t RESERVED0[1];

__IO uint32_t PIO2_0; /*!< Offset: 0x008 (R/W) I/O configuration for pin PIO2_0/DTR/SSEL1 */

__IO uint32_t RESET_PIO0_0; /*!< Offset: 0x00C (R/W) I/O configuration for pin RESET/PIO0_0 */

__IO uint32_t PIO0_1; /*!< Offset: 0x010 (R/W) I/O configuration for pin PIO0_1/CLKOUT/CT32B0_MAT2 */

__IO uint32_t PIO1_8; /*!< Offset: 0x014 (R/W) I/O configuration for pin PIO1_8/CT16B1_CAP0 */

uint32_t RESERVED1[1];

__IO uint32_t PIO0_2; /*!< Offset: 0x01C (R/W) I/O configuration for pin PIO0_2/SSEL0/CT16B0_CAP0 */

__IO uint32_t PIO2_7; /*!< Offset: 0x020 (R/W) I/O configuration for pin PIO2_7 */

__IO uint32_t PIO2_8; /*!< Offset: 0x024 (R/W) I/O configuration for pin PIO2_8 */

__IO uint32_t PIO2_1; /*!< Offset: 0x028 (R/W) I/O configuration for pin PIO2_1/nDSR/SCK1 */

__IO uint32_t PIO0_3; /*!< Offset: 0x02C (R/W) I/O configuration for pin PIO0_3 */

__IO uint32_t PIO0_4; /*!< Offset: 0x030 (R/W) I/O configuration for pin PIO0_4/SCL */

__IO uint32_t PIO0_5; /*!< Offset: 0x034 (R/W) I/O configuration for pin PIO0_5/SDA */

__IO uint32_t PIO1_9; /*!< Offset: 0x038 (R/W) I/O configuration for pin PIO1_9/CT16B1_MAT0 */

__IO uint32_t PIO3_4; /*!< Offset: 0x03C (R/W) I/O configuration for pin PIO3_4 */

LPC1114输入输出端口GPI 相关文章:

- LPC1114通用输入/输出端口(GPIO)(11-13)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)