Cortex-M3 (NXP LPC1788)之IIS控制器

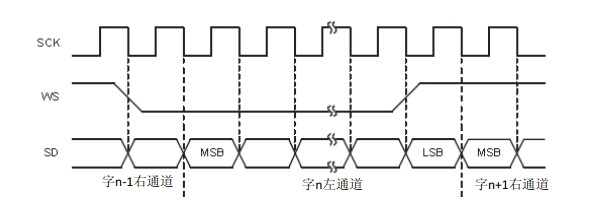

图1:I2S时序

从图中可以看出每个串行时钟SCK传送一位音频信号,因此SCK的频率=声道数X采样频率X采样位数。如程序中44.1KHZ采样的16位立体音,对应的SCK频率为2X16X44100HZ。WS是字段选择,也称为帧时钟,他的一个周期正好传输一帧数据。在WS改变后,数据字在发送时钟的下一个下降沿上开始。即图中MSB位在WS下降沿的下一个SCK时钟出现。在立体声模式下,当WS为低电平时发送左声道数据,当WS为高电平时发送右声道数据。如果是单声道模式,相同的数据会在WS的高低电平各发送一次。因此,要正确的通过I2S总线进行音频信号的传送,关键要正确配置传输速率。对于LCP1778,我们通过配置数字音频输出寄存器I2SDAO配置音频数据的宽度、声道数、和WS的周期。程序中的音频数据为44.1KHZ采样的16位立体音,因此I2SDAO中的WS_halfperiod字段配置成16-1,因为WS低电平和高电平各发送16位数据。配置SCK要设置2个寄存器,首先配置发送时钟速率寄存器I2STXRATE,通过它配置分数速率发生器以分频CCLK得到I2S TX_REF=CCLKX(X/Y)/2;如果我们使能了MCLK输出时,RX_REF就发送到MCLK管脚。其次,配置位发送时钟位速率寄存器I2STXBITRATE,该寄存器的值加1用来分频TX_REF得到SCK频率。

对I2S控制器配置完成后,我们可以将要发送的音频数据写入发送FIFO,FIFO的大小为8个字。而且发送和接收通道仅接收32位对齐的数据,因此对较短的数据我们要进行扩展才能写入FIFO进行发送。

对于总线上的状态,将在状态反馈寄存器I2SSTATE中进行指示,主要有中断和DMA请求的指示以及FIFO的当前深度指示。对于中断我们可以配置中断请求控制寄存器I2SIRQ设置FIFO触发中断的深度。

Cortex-M3NXPLPC1788IIS控制 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)