S3C2440系统中断

时间:11-20

来源:互联网

点击:

蓝牙模块,各种传感器,WIFI无线通信模块,这些硬件也要产生中断让CPU来处理数据,因此这些外设硬件通过中断信号线连接到中断控制器上,它们产生的中断叫做外部中断信号。它们有着和内部中断一样的处理机制,只不过,它没有一个固定的中断号与之对应,硬件与嵌入式系统的连接方式与中断处理完全由系统硬件与软件设计者实现。

外设硬件通过输入输出接口I/O Ports挂接到嵌入式系统上,I/O Ports向外设提供外部中断信号线,输出电源,频率时钟和输入输出信号线,外部硬件根据自己需要连接到I/O Ports上,产生中断时向外部中断信号线上送出中断信号,通过外部中断信号线传递到中断控制器。

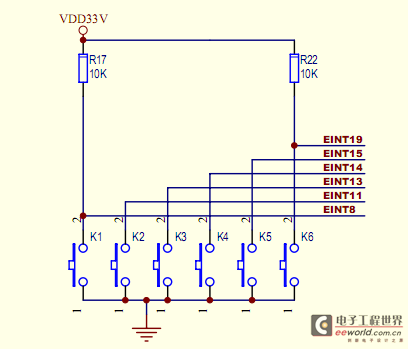

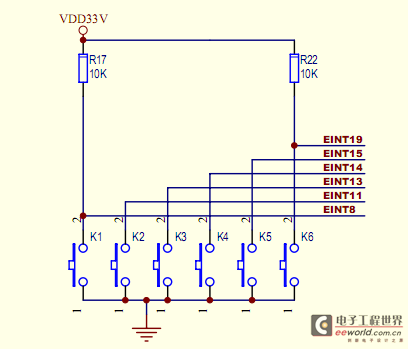

按键Key可以认为最为简单的一种硬件设备了,如下图所示:

图3-6按键硬件接线原理图

它功能很简单,可以将电路接通,按键K1~K6一端接地为低电平,另外一端接电源正极为高电平,EINT8,EINT11,EINT13,EINT14,EINT15,EINT19六根中断信号线分别和高电平端按键相连,当按键按下时电路接通,整个电路变成低电平,中断信号线上电压产生变化,通过设置中断触发方式,产生外部中断请求,输入到CPU内部,从而实现按键中断控制。

S3C2440A可以支持EINT0~EINT23共24种外部中断,完全可以满足小型嵌入式设备外设硬件的需求。

外部中断源也分为外部中断源和外部子中断源,其处理方式和内部中断源基本一样。

S3C2440A支持60种中断,多个硬件可能同时产生中断请求,由于CPU只能处理一个中断,中断控制器怎么选择出一个最佳的中断,交给ARM内核进行处理呢?中断控制器采用优先级仲裁比较的方式进行选择,找出优先级最高的中断源。中断控制器将60种中断源分成7组,如下图所示,它类似体育赛事里的比赛方式,所有参赛选手在小组赛PK,选择出小组赛最优秀选手,然后进入决赛阶段和其它小组最优先选择再PK,最后优胜者就是总冠军。其中ARBITER0~ARBITER5为“小组赛”阶段,中断源信号在各自小组里进行优先级仲裁,选择出最高优先级中断信号,每小组选出的中断信号送到ARBITER6,也就是决赛阶段,选择出最高优先级中断信号,交给ARM内核。

图3-7S3C2440优先级仲裁示意图

中断信号在7个分组里PK时的优先级是可编程的,通过PRIORITY寄存器进行优先级设置。如下表(只列出PRIORITY寄存器部分位):

表3-6中断优先级控制寄存器(PRIORITY)

通过设置仲裁组n优先级排序方式位,设置每个仲裁组内中断信号的优先级顺序,比如:ARB_SEL5分组时包含四个中断信号:REQ1 INT_UART0, REQ2 INT_SPI1, REQ3 INT_RTC, REQ4 INT_ADC,ARB_SEL5位采用默认值:00,当INT_UART0和INT_RTC中断信号同时产生时,INT_UART0会被选出,通过可编程方式改变优先级排序方式来改变中断信号优先级。

ARB_MODE0~ ARB_MODE6为每个仲裁分组的优先级轮转设置位,采用默认值时,当前中断信号被选择处理之后,再次产生中断请求时,它的优先级自动轮转到该组最低,这样可以保证优先级低的中断信号可以被及时处理,不至于出现优先级高且中断请求频繁的中断每次都被优先处理,而优先级低的被“饿死”的情况。显然,这种方式更民主,实时性更佳。

表3-7子中断源暂存寄存器(SUBSRCPND)

该寄存器用来标识保存子中断源信号,当某个子中断信号产生之后,SUBSRCPND对应位被自动置1,该位会一直保持被置位,只到中断处理程序将其清除为止,需要注意一下,清除中断是通过向对应位写入1来清除,而不是写入0,写入0无效。

(2)INTSUBMSK子中断源屏蔽寄存器

表3-8子中断源屏蔽寄存器(INTSUBMSK)

外设硬件通过输入输出接口I/O Ports挂接到嵌入式系统上,I/O Ports向外设提供外部中断信号线,输出电源,频率时钟和输入输出信号线,外部硬件根据自己需要连接到I/O Ports上,产生中断时向外部中断信号线上送出中断信号,通过外部中断信号线传递到中断控制器。

按键Key可以认为最为简单的一种硬件设备了,如下图所示:

图3-6按键硬件接线原理图

它功能很简单,可以将电路接通,按键K1~K6一端接地为低电平,另外一端接电源正极为高电平,EINT8,EINT11,EINT13,EINT14,EINT15,EINT19六根中断信号线分别和高电平端按键相连,当按键按下时电路接通,整个电路变成低电平,中断信号线上电压产生变化,通过设置中断触发方式,产生外部中断请求,输入到CPU内部,从而实现按键中断控制。

S3C2440A可以支持EINT0~EINT23共24种外部中断,完全可以满足小型嵌入式设备外设硬件的需求。

外部中断源也分为外部中断源和外部子中断源,其处理方式和内部中断源基本一样。

1.1.1中断优先级

S3C2440A支持60种中断,多个硬件可能同时产生中断请求,由于CPU只能处理一个中断,中断控制器怎么选择出一个最佳的中断,交给ARM内核进行处理呢?中断控制器采用优先级仲裁比较的方式进行选择,找出优先级最高的中断源。中断控制器将60种中断源分成7组,如下图所示,它类似体育赛事里的比赛方式,所有参赛选手在小组赛PK,选择出小组赛最优秀选手,然后进入决赛阶段和其它小组最优先选择再PK,最后优胜者就是总冠军。其中ARBITER0~ARBITER5为“小组赛”阶段,中断源信号在各自小组里进行优先级仲裁,选择出最高优先级中断信号,每小组选出的中断信号送到ARBITER6,也就是决赛阶段,选择出最高优先级中断信号,交给ARM内核。

图3-7S3C2440优先级仲裁示意图

中断信号在7个分组里PK时的优先级是可编程的,通过PRIORITY寄存器进行优先级设置。如下表(只列出PRIORITY寄存器部分位):

表3-6中断优先级控制寄存器(PRIORITY)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| PRIORITY | 0x4A00000C | R/W | 中断优先级控制寄存器 | 0x7F |

| PRIORITY | 位 | 描述 | 初始值 |

| ARB_SEL6 | [20:19] | 仲裁组6优先级排序方式 00 = REQ 0-1-2-3-4-5 01 = REQ 0-2-3-4-1-5 10 = REQ 0-3-4-1-2-5 11 = REQ 0-4-1-2-3-5 | 0x00 |

| ARB_SEL5 | [18:17] | 仲裁组5优先级排序 00 = REQ 1-2-3-4 01 = REQ 2-3-4-1 10 = REQ 3-4-1-2 11 = REQ 4-1-2-3 | 00 |

| … | … | … | … |

| ARB_MODE6 | [6] | 仲裁组6优先级是否轮转: 0 =不轮转,1 =轮转 | 1 |

| ARB_MODE5 | [5] | 仲裁组5优先级是否轮转: 0 =不轮转,1 =轮转 | 1 |

| … | … | … | … |

通过设置仲裁组n优先级排序方式位,设置每个仲裁组内中断信号的优先级顺序,比如:ARB_SEL5分组时包含四个中断信号:REQ1 INT_UART0, REQ2 INT_SPI1, REQ3 INT_RTC, REQ4 INT_ADC,ARB_SEL5位采用默认值:00,当INT_UART0和INT_RTC中断信号同时产生时,INT_UART0会被选出,通过可编程方式改变优先级排序方式来改变中断信号优先级。

ARB_MODE0~ ARB_MODE6为每个仲裁分组的优先级轮转设置位,采用默认值时,当前中断信号被选择处理之后,再次产生中断请求时,它的优先级自动轮转到该组最低,这样可以保证优先级低的中断信号可以被及时处理,不至于出现优先级高且中断请求频繁的中断每次都被优先处理,而优先级低的被“饿死”的情况。显然,这种方式更民主,实时性更佳。

2中断控制器相关寄存器

(1)SUBSRCPND子中断源暂存寄存器表3-7子中断源暂存寄存器(SUBSRCPND)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| SUBSRCPND | 0x4A000018 | R/W | 子中断源暂存寄存器,保存中断请求状态: 0:没有中断请求信号 1:中断请求信号产生 | 0x00000000 |

| SUBSRCPND | 对应SRCPND | 位 | 描述 | 初始值 |

| Reserved | 无 | [31:15] | 未使用 | 0 |

| INT_AC97 | INT_WDT_AC97 | [14] | 0 =未产生中断1 =产生中断 | 0 |

| … | … | … | … | … |

| INT_RXD0 | INT_UART0 | [0] | 0 =未产生中断1 =产生中断 | 0 |

该寄存器用来标识保存子中断源信号,当某个子中断信号产生之后,SUBSRCPND对应位被自动置1,该位会一直保持被置位,只到中断处理程序将其清除为止,需要注意一下,清除中断是通过向对应位写入1来清除,而不是写入0,写入0无效。

(2)INTSUBMSK子中断源屏蔽寄存器

表3-8子中断源屏蔽寄存器(INTSUBMSK)

S3C2440系统中 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)