五大ARM存储器之一:协处理器CP15

指令Cache相关属性类中指定的属性,其具体编码参见表7。

表7 Cache类型标识符寄存器属性字段含义

编 码

0b0000

0b0001

0b0010

0b0110

0b0111

S位:定义系统中的数据Cache和指令Cache是分开的还是统一的。如果S=0,说明指令Cache和数据Cache是统一的,如果S=1,则说明数据Cache和指令Cache是分离的。

数据Cache相关属性:定义了数据Cache容量、行大小和相联(associativity)特性(如果S≠0)。

指令Cache相关属性:定义了指令Cache容量、行大小和相联(associativity)特性(如果S≠0)。

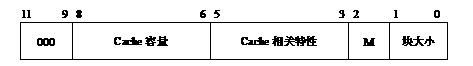

数据Cache相关属性和指令Cache相关属性分别占用控制字段[23:12]和[11:0],它们的结构相同,图6以指令Cache为例,显示了编码结构。

图6 指令Cache编码结构

其中,各部分的含义说明如下。

bit[11:9]:保留用于将来使用。

bit[8:6]:定义Cache的容量,其编码格式及含义如表8所示。

表8 类型标识符寄存器控制字段bit[8:6]含义

编 码

0b000

0b00

0b010

0b011

0b100

0b101

0b110

0b111

bit[1:0]:定义Cache的块大小,其编码格式及含义如表9所示。

表9 类型标识符寄存器控制字段bit[1:0]含义

编 码

0b00

0b01

0b10

0b11

bit[5:3]:定义了Cache的相联属性,其编码格式及含义如表10所示。

表10 类型标识符寄存器控制字段bit[5:3]含义

0b001

0b010

0b011

0b1001

0b101

0b110

0b111

1.4 寄存器c1

CP15中的寄存器c1包括以下控制功能:

· 禁止/使能MMU以及其他与存储系统有关的功能;

· 配置存储系统以及ARM处理器中相关的工作。

注意在寄存器c1中包含了一些没有使用的位,这些位在将来可能被扩展其他功能时使用。因此为了编写代码在将来更高版本的ARM处理器中仍可以使用,在修改寄存器c1中的位时应该使用“读取-修改特定位-写入”的操作序列。

例2用MRC/MCR指令将协处理器寄存器c1的值进行读取和写入。

MRC P15,0,r0,c1,0,0 ;将寄存器c1的值读取到ARM寄存器r0中

MCR P15,0,r0,c1,0,0 ;将ARM寄存器r0的值写入寄存器c1

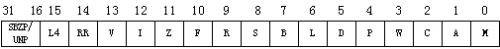

图7显示了寄存器c1的编码格式。

图7 寄存器c1编码格式

寄存器c1各控制字段的含义如表11所示。

表11 寄存器c1中各控制位字段的含义

C1中的控制位含 义

M(bit[0])禁止/使能MMU或者MPU

0:禁止MMU或者MPU

1:使能MMU或者MPU

如果系统中没有MMU或者MPU,读取时该位返回0,写入时忽略

A(bit[1])对于可以选择是否支持内存访问时地址对齐检查的系统,本位禁止/使能地址对齐检查功能

0:禁止地址对齐检查功能

1:使能地址对齐检查功能

对寄存器进行写操作时,忽略该位

C(bit[2])当数据Cache和指令Cache分开时,本控制位禁止/使能数据Cache。

当数据Cache和指令Cache统一时,该控制位禁止/使能整个Cache

0:禁止Cache

1:使能Cache

如果系统中不含Cache,读取时该位返回0,写入时忽略

当系统中Cache不能禁止时,读取返回1,写入时忽略

W(bit[3])禁止/使能写缓存

0:禁止写缓存

1:使能写缓存

如果系统中不含写缓存,读取时该位返回0,写入时忽略

当系统中的写缓存不能禁止时,读取时该位返回0,写入时忽略

P(bit[4])对于向前兼容26位ARM处理器,本控制位控制PRGC32控制信号

0:异常中断处理程序进入32位地址模式

1:异常中断处理程序进入26位地址模式

如果系统不支持向前兼容26位地址,读取该位时返回1,写入时被忽略

D(bit[5])对于向前兼容26位ARM处理器,本控制位控制DATA32控制信号

0:禁止26位地址异常检查

1:使能26位地址异常检测

如果系统不支持向前兼容26位地址,读取该位时返回1,写入时被忽略

L(bit[6])对于ARMv3及以前版本,本控制位可以控制处理器的中止模式

0:选择早期中止模式

1:选择后期中止模式

对于以后的处

ARM存储器协处理器CP1 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)