ARM Cortex-M3 学习笔记(2)

时间:11-20

来源:互联网

点击:

最近在学ARM Cortex-M3,找了本号称很经典的书“An Definitive Guide to The ARM Cortex-M3”在看。这个系列学习笔记其实就是在学习这本书的过程中做的读书笔记。

内核寄存器组包括R0-R15,R0-R12是通用寄存器,部分Thumb指令只能访问R0-R7。

R13是堆栈指针,实际上有两个,一个是主堆栈指针(MSP)另一个是进程堆栈指针(PSP),堆栈要求4字节对齐。

R14存放程序的返回地址。

R15是PC,记录程序当前的执行地址。

特殊功能寄存器包括:

程序状态字寄存器组(PSRs)

中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)

控制寄存器(CONTROL)

运行模式和特权级别

两种运行模式:handler mode和thread mode。

两种特权级别:特权级和用户级

中断例程工作在特权级,普通程序代码既可以工作在特权级也可以在用户级。

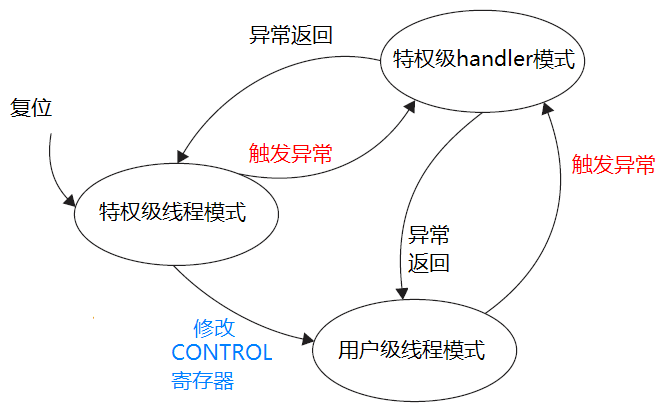

相互间的转换用下图来描述:

第二章 Cortex-M3 概述

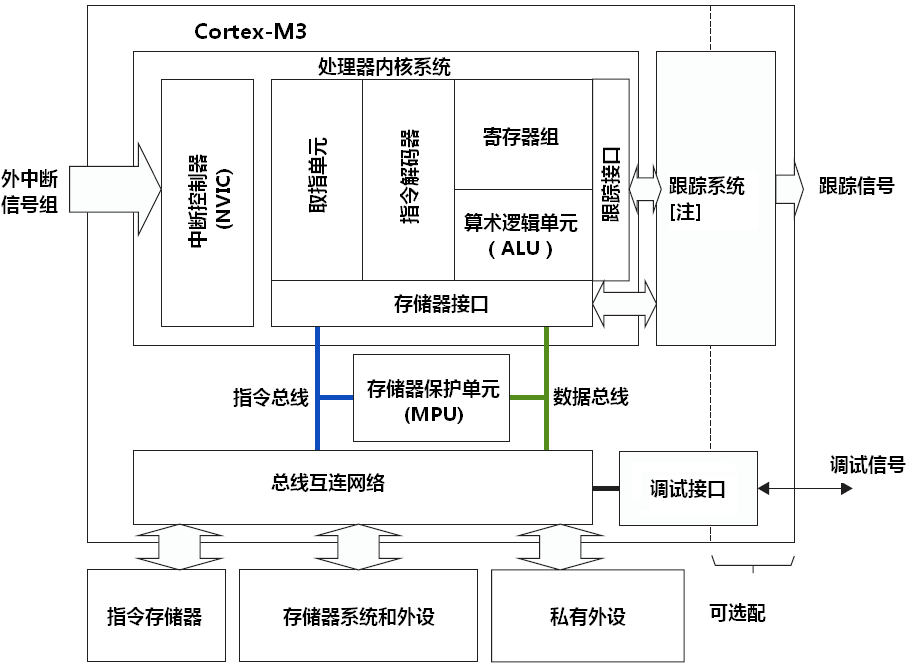

Cortex M3 内核的组成可以用一张简图来表示:

内核寄存器组包括R0-R15,R0-R12是通用寄存器,部分Thumb指令只能访问R0-R7。

R13是堆栈指针,实际上有两个,一个是主堆栈指针(MSP)另一个是进程堆栈指针(PSP),堆栈要求4字节对齐。

R14存放程序的返回地址。

R15是PC,记录程序当前的执行地址。

特殊功能寄存器包括:

程序状态字寄存器组(PSRs)

中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)

控制寄存器(CONTROL)

运行模式和特权级别

两种运行模式:handler mode和thread mode。

两种特权级别:特权级和用户级

中断例程工作在特权级,普通程序代码既可以工作在特权级也可以在用户级。

相互间的转换用下图来描述:

图 4 操作模式转换图

嵌套向量中断控制器NVIC(Nested Vectored Interrupt Controller)

? 可嵌套中断支持

? 向量中断支持

? 动态优先级调整支持

后面有一章会对NVIC进行详细的介绍。

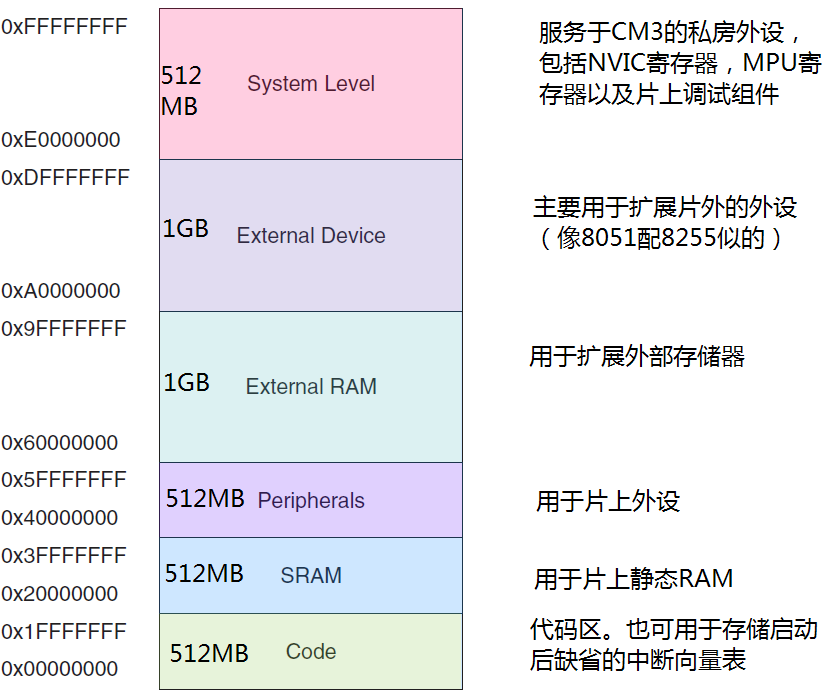

地址空间分配

与以前的ARM 内核不同,Cortex-M3对地址空间的分配有个大的框架。向NVIC寄存器等的地址也都被固定了下来,这就方便了在程序的移植。具体的地址分配可以用下图来简单的描述:

图 5 地址分配

总线

Cortex-M3内部有若干个总线接口,以使Cortex-M3能同时读取程序代码和访问内存,它们是:

指令存储区总线(两条)

系统总线

私有外设总线

中断和异常

Cortex-M3支持11个内部异常和240个外部中断。当然,对具体的芯片,可以支持的外部中断数量肯定就要少的多了。

调试支持

在支持传统的JTAG基础上,还支持更新更好的串行线调试接口。

基于CoreSight调试解决方案,使得处理器哪怕是在运行时,也能访问处理器状态和存储器内容。

内建了对多达6个断点和4个数据观察点的支持。

ARMCortex-M 相关文章:

- 让ARM Cortex-M7再想一一会儿(11-26)

- ARM CORTEX-M3 内核架构理解归纳(11-21)

- ARM Cortex-M3 内核介绍(11-21)

- ARM Cortex-M3 学习笔记(4-4)(11-20)

- ARM Cortex-M3 学习笔记(4-5)(11-20)

- ARM Cortex-M3 学习笔记(4-6)(11-20)