ARM Cortex-M3 学习笔记(6)

第六章 Cortex-M3的全景概貌

这一章的内容大体有个了解就行了,后面章节中会对这里讲到的各个部分深入讲解。

3级流水线,流水线的3个级分别是:取指,解码和执行

Cortex M3 内部构成可以用下面的这个框图来说明。

图 1 Cortex-M3内部框图

各个部件的简单介绍如下。

NVIC:嵌套向量中断控制器

SYSTICK Timer:一个简易的周期定时器,用于提供时基,亦被操作系统所使用

MPU:存储器保护单元(可选)

CM3BusMatrix:内部的AHB互连

AHB to APB:把AHB转换为APB的总线桥

SW-DP/SWJ-DP:串行线调试端口/串行线JTAG 调试端口。通过串行线调试协议或者是传统的JTAG协议(专用于SWJ-DP),都可以用于实现与调试接口的连接

AHB-AP:AHB访问端口,它把串行线/SWJ接口的命令转换成AHB数据传送

ETM:嵌入式跟踪宏单元(可选组件),调试用。用于处理指令跟踪

DWT:数据观察点及跟踪单元,调试用。这是一个处理数据观察点功能的模块

ITM:仪器化跟踪宏单元

TPIU:跟踪单元的接口单元。所有跟踪单元发出的调试信息都要先送给它,它再转发给外部跟踪捕获硬件的。

FPB:Flash地址重载及断点单元。

ROM表:一个小的查找表,其中存储了配置信息。

这里给出个Cortex-M3内核与其他片内外设的连接示例。

图 2 Cortex-M3总线连接样板范例

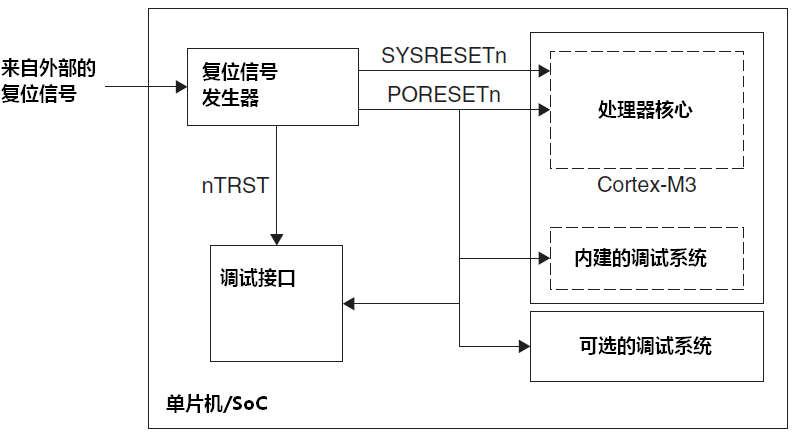

Cortex-M3 内核有三种复位信号,分别如下:

复位信号 | 描述 |

上电复位(nPORESET) | 在器件上电时需要把复位置为有效(assert),把处理器核心和调试系统一起复位 |

系统复位(nSYSRESET) | 只影响处理器核心、NVIC(与调试相关的除外)以及MPU,不复位调试系统 |

测试复位(nTRST) | 只复位调试系统 |

这些复位信号在芯片内部的流向与作用见下图。

图 3 典型的Cortex-M3芯片内部复位信号和其作用范围示意图

ARMCortex-M 相关文章:

- 让ARM Cortex-M7再想一一会儿(11-26)

- ARM CORTEX-M3 内核架构理解归纳(11-21)

- ARM Cortex-M3 内核介绍(11-21)

- ARM Cortex-M3 学习笔记(4-4)(11-20)

- ARM Cortex-M3 学习笔记(4-5)(11-20)

- ARM Cortex-M3 学习笔记(4-6)(11-20)