LPC2103学习之PLL

PLL的概述:

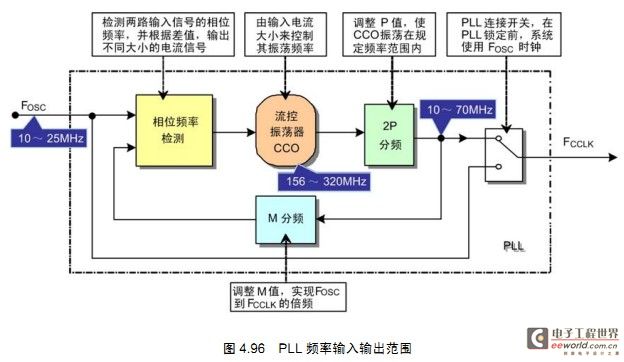

PLL它本来接收的输入时钟频率范围仅为10MHz~25MHz,然后可以通过一个振荡器(CCO)倍增到范围10MHz~70MHz。倍频器可以是1到32的一个整数,不过实际上没那么多,因为跟LPC2103具体的最大工作频率相关。最高频率为70MHz。CCO的操作频率为156MHz~320MHz。故在PLL内部还有一个额外的分频器在PLL提供所需要的输出频率时使CCO保持在其频率范围。输出分频器可以设置为2、4、8、16分频产生输出时钟。下图展示了PLL的内部逻辑原理。

PLL激活由PLLCON寄存器控制,PLL倍频器和分频器的值由PLLCFG寄存器控制。由于芯片的所有操作都依赖于PLL(包括看门狗),如果操作PPL错误的话,将引起后续的执行错误。所以我们需要对它进行保护,保护的操作类似于操作看门狗定时器的馈送序列来实现。PLL在芯片复位时和进入掉电模式后关闭并旁路。PLL的使能只能通过软件实现。程序必须在配置并激活PLL后等待其锁定,然后作为时钟源连接到PLL。

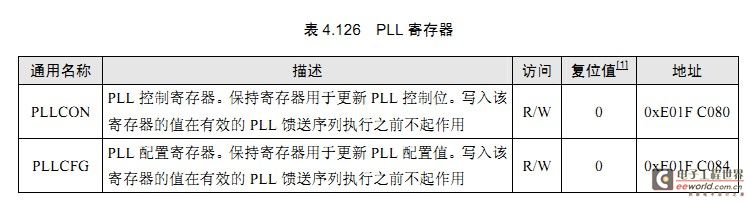

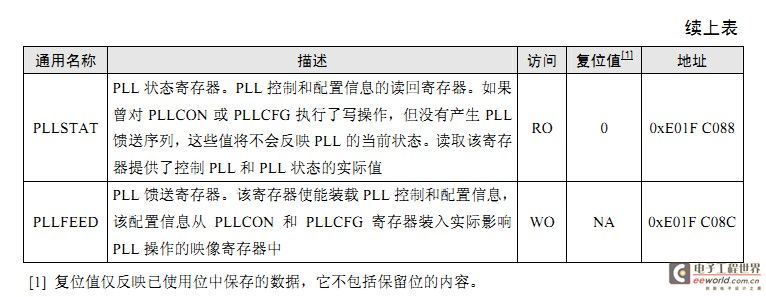

下面就是PLL的相关寄存器,不多,只有4个。

1。选择需要操作的处理器操作频率(CCLK),根据处理器的整体要求等各方面来设定。外围器件的时钟频率可以低于处理器频率。

2.选择振荡器频率(Fosc)。CCLK一定是Fosc的整数倍。

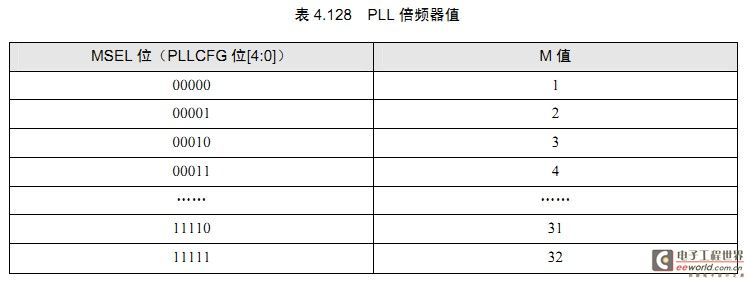

3.计算M值匹配MSEL位。M = CCLK/Fosc。M的取值范围为1~32,在PLLCFG中,写入MSEL的值为M-1.

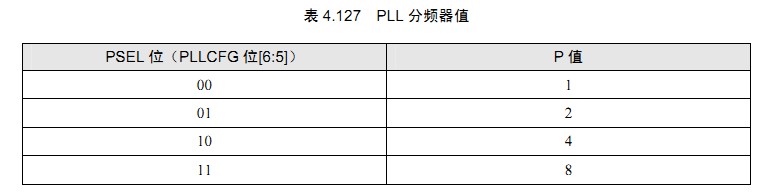

4.选择P值以配置PSEL位,使Fcco在定义的限制频率范围内。P必须是1、2、4或8其中的一个。写入PPCFG中PSEL的值见下表。

PLL的操作也有两种方式。

一是.查询方式

1.PLLCON=1,设定PLL之前,需使能PLL,但不能连接PLL。

2.设定P和M的值(PLLCFG)

3.发送PLL馈送序列。

4.等待PLL锁定--PLLSTAT.10 = 1.

5.PLLCON=3,设定P和M之后,连接PLL。

6.发送PLL馈送序列,把P和M的值写入硬件。

二是中断方式

1.PLLCON=1,设定PLL之前,需使能PLL,但不能连接PLL。

2.设定P和M的值(PLLCFG)

3.发送PLL馈送序列。

PLL中断服务程序:

4.PLLCON=3,设定P和M之后,连接PLL。

5.发送PLL馈送序列,把P和M的值写入硬件。

6.禁止PLL中断,返回。

LPC2103PL 相关文章:

- LPC2103之PLL寄存器(11-29)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)