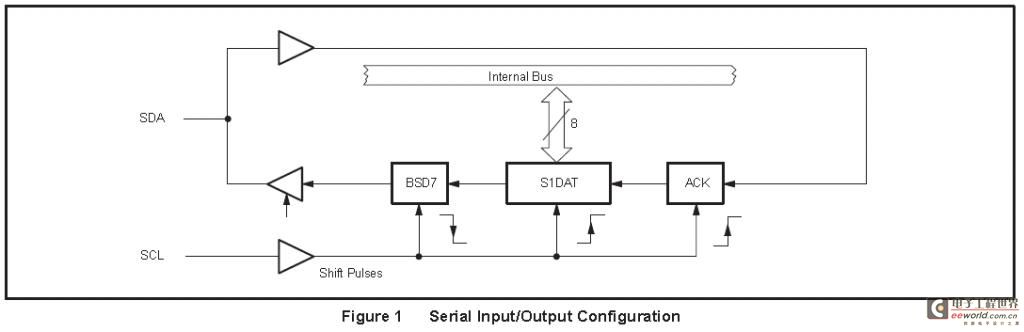

I2C总线串行输入输出结构

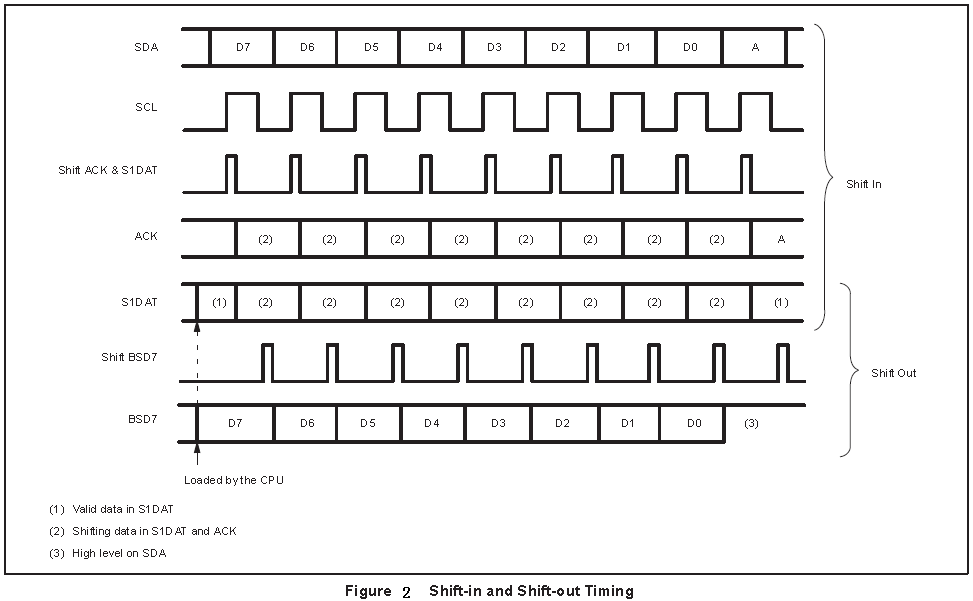

IIC总线的串行输入输出结构保证了IIC总线的数据寄存器中能保存总线上的最新数据。SDAT和ACK组成一个9为的移位寄存器,它组成一个环状结构。串行输出的同时不断采入总线上的数据。ACK标志位由总线控制,并可以由CPU存取(存入1对应的是非应答,存入0对应的应答)。在SCL线上的时钟脉冲的上升沿,串行数据通过ACK标志位存入SDAT,串行数据在SCL时钟脉冲下降沿沿BSD7移出当一个字节数据移入SADT后,SDAT中的数据有效,控制逻辑在第9个时钟脉冲周期送出应答位。

为什么IIC总线进行数据发送时,时钟信号为高电平期间,数据线上的数据必须保持数据稳定???这是因为会在高电平期间采集总线上的数据,如果此时总线上的数据不稳定,会导致采集的数据和发送的数据不一致,从而关闭发送(类似仲裁失败)。协议规定只有在时钟信号为低电平期间,数据线上的高电平或低电平才允许变化,这是因为BSD7中的数据是在时钟下降沿发出的,且不会在时钟脉冲低电平期间采集总线上的数据。

在CPU对SDAT写入时,SDAT7装入BSD7,这是向SDA线上发送的第一位数据,9个时钟脉冲后SADT中的8位数据发送到SAD线上,应答位出现在ACK中,这样发送到总线上的数据又返回到SDAT中。

SDA寄存器,包含个待发送的数据或一个刚收到的数据字节,发送时,数据总是从右向左移位。数据移出时,总线上的数据同时移入,移位寄存器的这种结构保证了总线竞争失败时数据不会丢失。它以并行的方式与内部总线相连,以串行方式与SDA相连。发送数据时,由内部总线装入到SDAT中,发送时,数据以串行从串行通道返回SDAT中。接收时,装入新接收的SDA线上的数据。

I2C总线输入输出结 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)