单片机外部与内部时钟源的切换

XC2336B是Infineon的16位微控制器XC2000家族中的一员,它将功能和性能都得到扩展的C166SV2内核、功能强大的片上外设子系统和各种片上存储器进行了完美结合。执行速度更快、稳定性更好、操作更简单。

1 XC2336B单片机的时钟产生

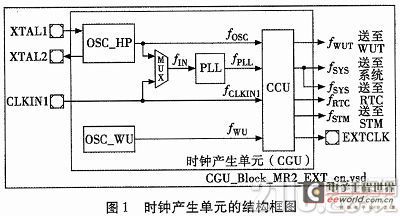

XC2336B单片机时钟产生单元(CGU)可非常灵活的产生单片机所需的时钟。通过锁相环(PLL),时钟产生单元(CGU)可将低频外部时钟转换为高频系统时钟,无需外部直接产生高频时钟。时钟产生单元(CGU)由时钟发生器和时钟控制单元(CCU)构成。

XC2336B单片机带有5 MHz的内部时钟源,可以在无外部时钟信号的情况下产生系统时钟(fsys)。该内部时钟源位于锁相环(PLL)单元中,通过对该单元的合理设置,即可完成该单片机的无晶振工作。但由此产生的系统时钟(fsys)受温度影响很大,时钟的精度不高,适合在简单的应用中使用。因此,常用的产生系统时钟 (fsys)的方法是,由高精度振荡器电路(OSC_HP)驱动一个外部晶振,产生的时钟信号送入锁相环(PLL)倍频后产生系统时钟(fsys)。振荡器电路包含一个反相放大器,以XTAL1为输入、XTAL2为输出。

在某些使用环境中,由于震动等原因,外部晶振有可能损坏。但是,在这种情况下,又不希望单片机处于死机状态,希望单片机能够发出一些报警信号,并能完成一些简单功能。那么,能否让单片机自动切换为内部时钟源工作呢?答案是肯定的。也就是要让单片机在正常状态下以高精度系统时钟运行,在外部晶振失效时以内部时钟源产生的系统时

钟运行,而且这两个系统时钟的值是一样的。

要完成XC2336B单片机外部与内部时钟源的切换,最主要的设置是对锁相环(PLL)的设置。因此我们先介绍一下XC2336B单片机的锁相环(PLL)。

2 锁相环PLL组成以及它的三种工作模式

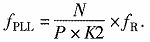

1)PLL由压控振荡器(VCO)和反馈通路组成。反馈通路上的分频器(N分频)对VCO频率分频,得到的结果和外部经P分频处理的参考频率进行比较。相位检测电路根据这两个时钟信号的差值相应控制VCO频率(fVCO)。PLL锁相检测单元监控并指示该状态。相位检测逻辑继续监控这两个时钟信号,如有需要则调整VCO时钟。PLL输出时钟fPLL由VCO时钟经K2分频产生、或由振荡器时钟经K1分频产生。

2)正常模式下,参考频率fR经P分频、N倍频和K2分频产生PLL时钟:

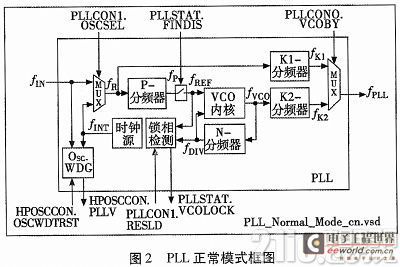

3)预分频模式下,参考频率fR经K1分频产生PLL时钟:

4)未锁相模式下,PLL以压控振荡器(VCO)基频fVCObase工作,fVCObase经K2分频产生PLL时钟:

3 实现外部与内部时钟源切换的步骤

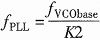

1)DAVE中的有关系统时钟的设定

先设为使用8 MHz的外部时钟源,最终的系统时钟频率fsys=80 MHz。系统时钟的输出管脚在调试完成后应该关闭,防止干扰产生。

2)在由DAVE和Keil生成的C语言文件中找到MAIN_vChangeFreq()函数,它就是锁相环(PLL)的配置函数。通过对该函数的修改,就可以实现外部与内部时钟源的切换。

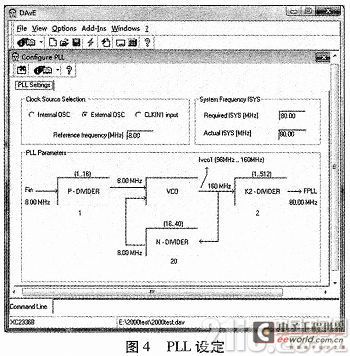

A、该函数初始的程序流程图如下:

在这种状态下,一旦外部晶振失效,CPU将处于死机状态,无任何信号输出。

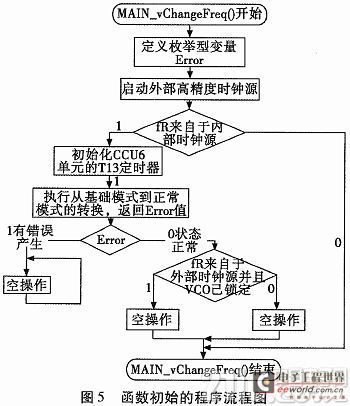

B、增加用户函数后,能够实现时钟源切换的函数MAIN_vChangeFreq()的流程图

在这种状态下,一旦外部晶振失效,CPU将执行用户函数,使CPU能够利用5MHz的内部时钟生成80 MHz的系统时钟。

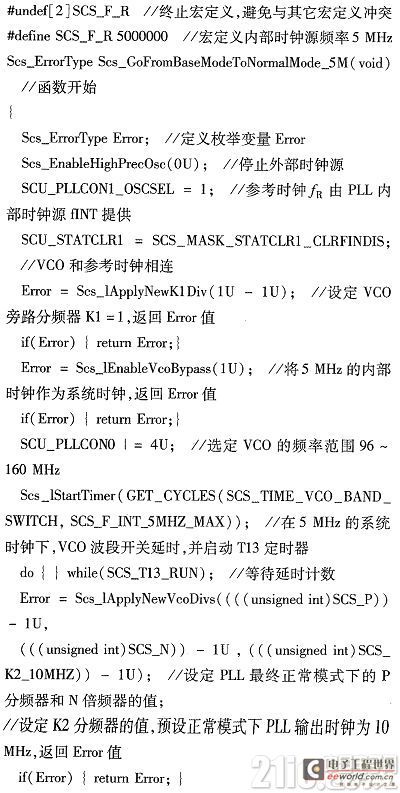

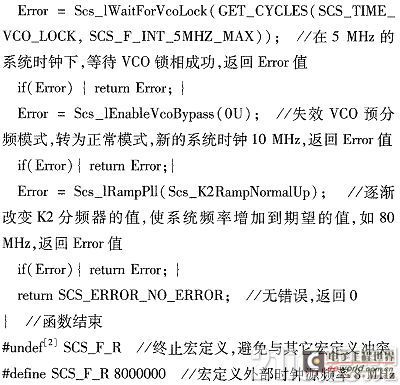

3)上个流程图中提到的用户函数代码如下:

函数说明:在外部时钟源失效的情况下,使fR来自于内部时钟源,PLL由上电基础模式(Fsys=10 MHz)或VCO预分频模式换到VCO正常模式,返回Error值

4 结束语

通过对由DAVE和Keil生成的MAIN_vChangeFreq()函数的修改,实现了单片机在正常状态下以高精度系统时钟运行,在外部晶振失效时以内部时钟源产生的系统时钟运行的工作模式。

单片机外部内部时钟 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)