s3c2410 的时钟设置

时间:11-23

来源:互联网

点击:

FCLK用于CPU核

HCLK 用于AHB总线设备

PCLK 由于APB总线上的设备

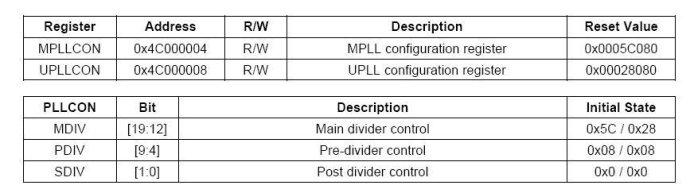

s3c2410需要设置的时钟寄存器包括:LOCKTIME、MPLLCON、CLKdivN。

其中LOCKTIME直接使用默认值就可以了。

MPLLCOM用于设置FCLK的时钟值,也就是主时锁存器。

MPLL(FCLK) = (m * Fin)/(p* 2^s);

m = (Mdiv + 8), p = (Pdiv + 2), s = Sdiv

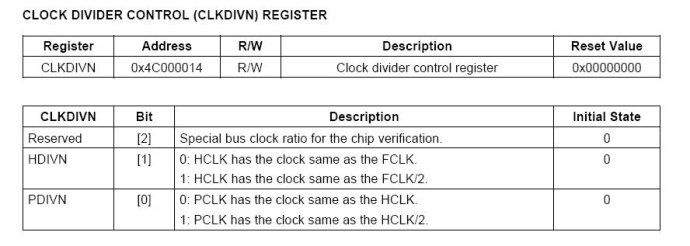

CLKdivN 用于设置FCLK、HCLK、PCLK三者的比例。

s3c2410的典型设置为

#define S3C2410_MPLL_200MHz ((0x5c < 12) | (0x04 < 4) | (0x00))

CLKdivN = 0x03; //这样的FCLK : HCLK : PCLK = 1: 2 :4

s3c2410时钟设 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)