调试时钟定时问题的思路

如今数字系统的稳定性和性能都是建立在其内部时钟系统之上。

由于时钟信号对系统性能影响很大,所以定位并纠正这些信号出现的问题非常重要。

工程师必须像一名优秀侦探员那样找出正确的测试问题并准确确定故障原因以及影响。

修正那些故障影响并非是一种最优的解决方法,它将导致遗漏故障原因,而在以后导致更严重的时序错误。

例如,在出现问题(大抖动、畸形波形或者没有达到设计参数要求)的时候发现一个正在冒烟的旁路滤波器,那么可以肯定地证明这是问题的原因,而不是其它潜在原因的证据。

可能的原因是电容在阻止某个频率上噪声的影响,但是却没有能够保护时钟器件不受噪声的影响。

一个正确设计的终端电路由于采用了不合适的源驱动器件阻抗而变得不正确,是另外一个很好的例子。

通常,50Ω的终端阻抗和50Ω的传输线阻抗对于最高级别的信号完整性是正确的,但并不总是如此。

最直接的方法是调整电路的终端,但这会改变连接驱动和终端的传输线的阻抗。实际上,最明显的原因经常和真正的原因相差很远。

最好的解决方法是通过选用合适的驱动器从问题的根本原因上解决问题,而不是浪费大量时序来调试终端以求得一个能够运行但并非最优的结果。通过纠正根本原因,你还可纠正其它一些不会引起时序冲突但能够破坏时序边界的小问题。

我们必须注意到时钟系统的故障不会由一个可很容易发现的单个原因引起的。一般这种故障是由好几个稍微不常见的原因引起,这些原因会导致时序边界越过限制。

例如,由非良好接地、不正确的旁路器件值以及不理想的走线拓扑导致的综合效应将产生足够噪声,从而引发系统故障。使事情更加糟糕的是时钟器件和设计的其他电路共享电源和地线平面。这样,时钟器件将受到它们所控制的系统环境的噪声影响。毫无疑问,找到这些问题的根源是非常困难的。

时域的方法

出现问题的时候首先要察看时域信息。时序位置的不正确表现为波形偏斜和延迟,使时序与期望值出现有规律性或无规律性的不同。这主要有两个根本原因:确定性抖动和随机抖动噪声。

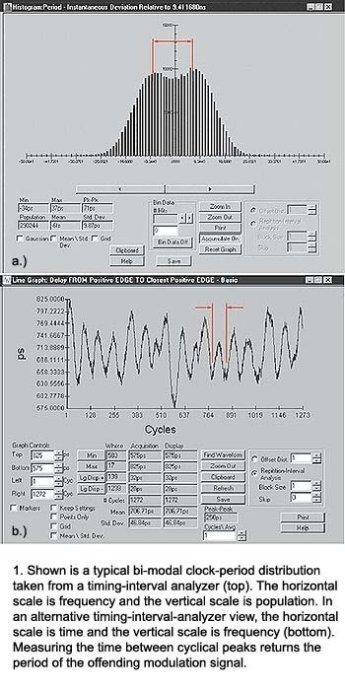

确定性的抖动肯定可以找到根本原因。时序位置的偏移是规律性地出现,并且可以查找出来。通过读出多模型分布测量(图1)中峰值时间的偏移,通常可以非常迅速地确定干扰信号的频率。找到频率以后,距离找到真正的原因就仅有几步之遥了。

随机抖动的问题稍微有点麻烦,它可能来自于器件本身或者是从其他器件传过来的。

频域的方法

另一个寻找时钟问题的角度是在频域中寻找。在频域中,我们同时观察频率及其周围的能量分布。时钟系统需要很快的上升时间以减少负载的转换时间。这给时钟信号的频谱带来许多奇次谐波。(一个具有无限快上升时间的纯矩形波的频谱是频率基频和所有奇次谐波之和)。

在频域,我们正在寻找其它时钟信号和所需时钟频率混合在一起的结果。

当时钟互相调制在一起的时候会带来四个混合部分:相加值,相减值以及两个原始频率。通常,干扰信号的频率和所需信号的频率离得很近,相加后的信号与相减后的信号也会如此。

调试时钟定时问 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)