ARM·电源电路/复位电路/GPIO

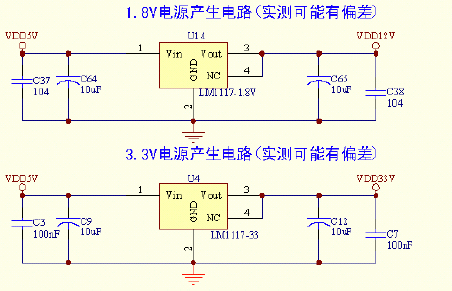

硬件电路,关于

LM117的输出电压的范围是1.25-37v连续可调,最大电流1.5A,三端可调线性稳压电路 ;

(这里不明白c9和c18这两个极性电容的作用)

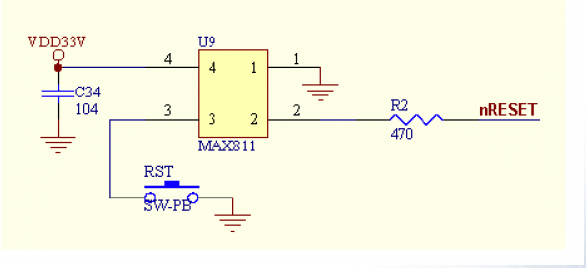

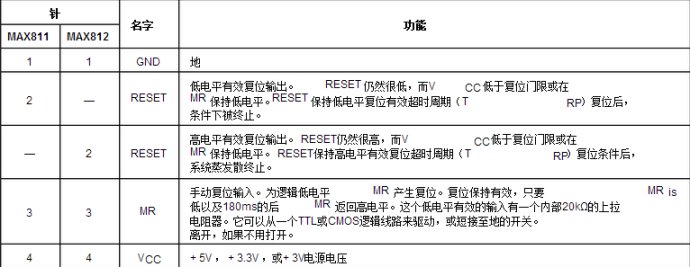

MAX811(4引脚的电压监视器)

引脚功能:

分析复位电路

引脚1——GND

引脚4——3.3v的VCC

(这里VCC和GND之间的104电容,是去耦电容,以后会经常遇到;一是作为集成电路的蓄能电容;二是滤除该器件产生的高频噪声,切断其功能回路传播的通路;三是防止电源携带的噪声对电路构成干扰)

引脚2——低电平复位有效输出,这是内部系统的软件复位;

引脚3——手动复位,也就是外部的复位按钮 ;

整个电路还算比较简单 ;

S3C2440A时钟控制逻辑通过外接晶振,给整个芯片提供三种时钟

FCLK:用于CPU核

HCLK:用于AHB(Advanced High Performance Bus)总线设备:CPU核、存储器控制、中断控制器、LCD控制器、DMA和USB主机模块等

PCLK:用于APB(Advanced Peripheral Bus)外围设备:WATCHDOG、IIS、IIC、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI等

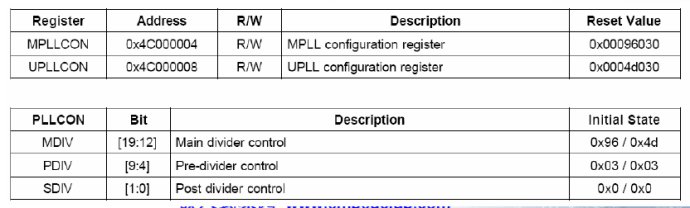

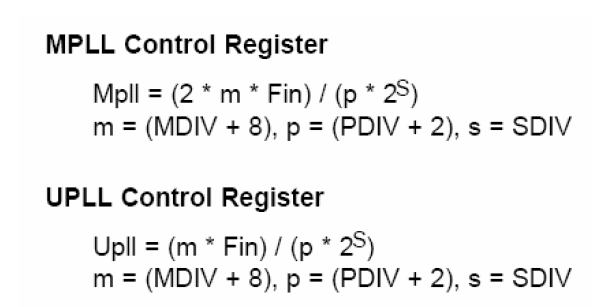

mini2440开发板外接晶振频率Fin为12MHz,需要通过时钟控制逻辑PLL提高系统时钟

S3C2440A有两个PLL(MPLL:用于设置FCLK、HCLK、PCLK

PLL参数推荐值

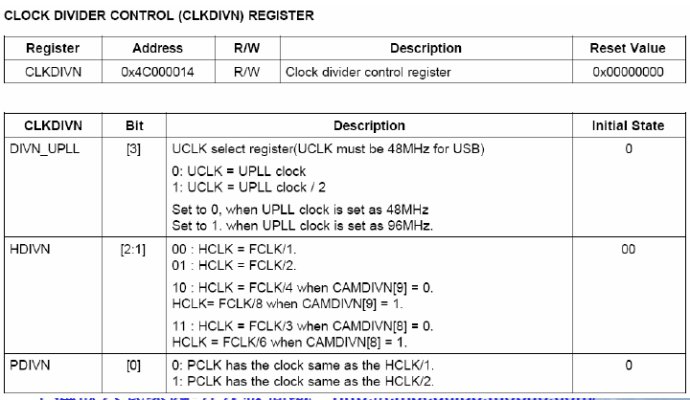

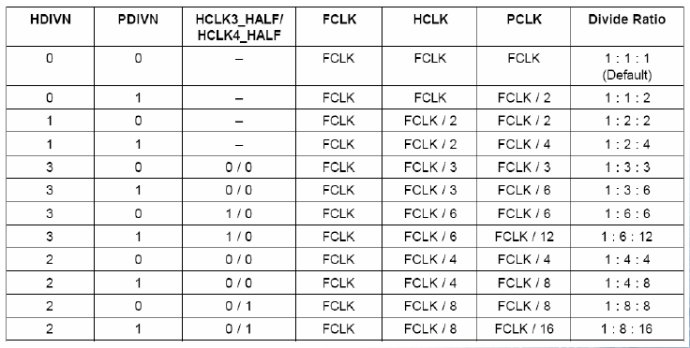

CLKdivN寄存器:分频系数寄存器(用于设置FCLK,HCLK,PCLK三者的比例)

*确认外部输入晶振频率Fin

*确定系统输出时钟频率FCLK

*对照PLL值推荐参数表,找到一租Mdiv、Pdiv和Sdiv,设置MPLLCON

*设置UPLLCON

*确定FCLK、HCLK、PCLK比例系数,设置时钟分频系数寄存器CLKdivN,从而确定当前系统下FCLK、HCLK、PCLK的频率值;

S3C2440A包含GPA-GPJ共9组端口

大部分管脚都是复用的,可通过相应的寄存器配置I/O模式

(GPA对应的控制寄存器:GPACON、GPADAT)

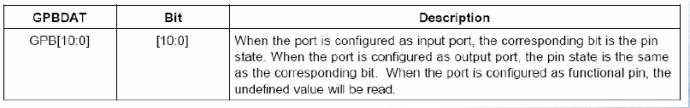

(GPB对应的控制寄存器:GPBCON、GPBDAT、GPBUP)

所谓复用:大部分I/O可以被配置为输入、输出模式还是其他特殊功能,且可以选择是否内部上拉 ;

GPIO的操作:

GPxCON—用于选择工作模式

GPxDAT—用于选择读/写数据(高低电平写数据01)

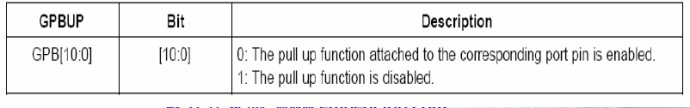

GPxUP—用于确定是否使用上拉电阻

ARM电源电路复位电路GPI 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)