S3C2440的时钟系统

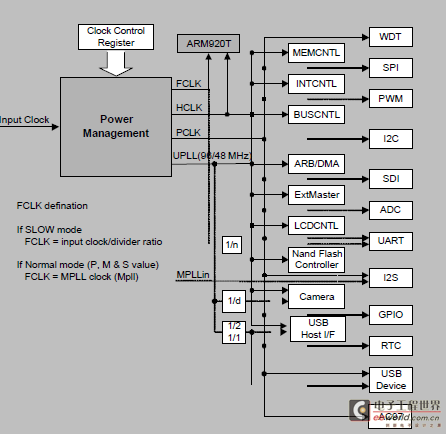

图中给出了各种接口设备使用的时钟信号

首先讲下FCLK,首先看下datasheet中的介绍:

The Clock control logic in S3C2440A can generate the required clock signals including FCLK for CPU, HCLK for the

AHB bus peripherals, and PCLK for the APB bus peripherals.

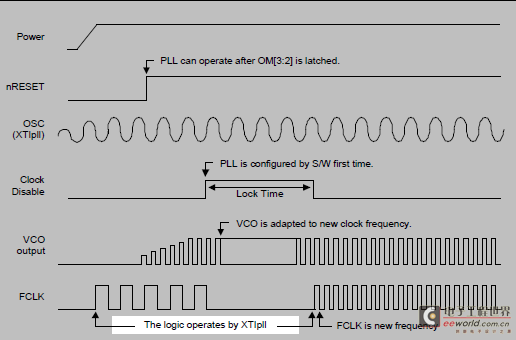

1、上电几毫秒后(power由低变高),晶振输出稳定,此时FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

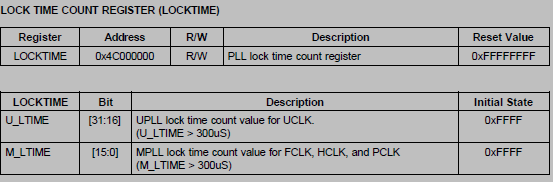

2、我们可以在程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

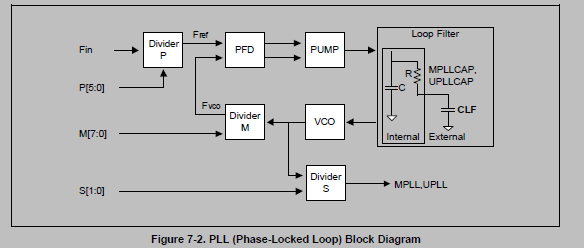

MPLLCON的输入输出频率间的关系为

UPLLCON的输入输出频率间的关系为

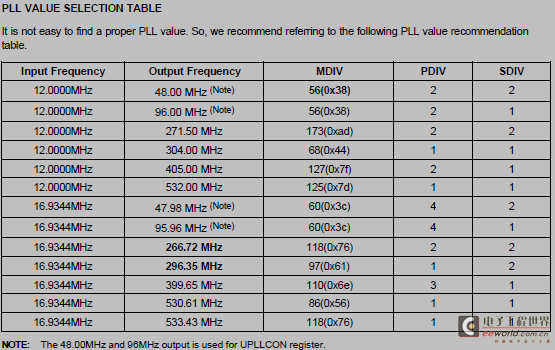

手工计算相对复杂些,我们可以根据欲得到的主频FCLK大小,直接通过查表来获知各倍频因子的设置参数。

对于12MHz的晶振,要想经过PLL电路得到405MHz,查表得应该设置Mdiv、Pdiv、Sdiv分别为0x7f、2、1。

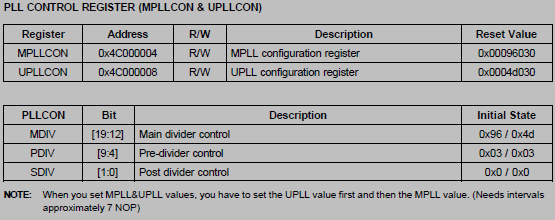

那在哪里设置Mdiv、Pdiv和Sdiv这3个值呢,还是datasheet:

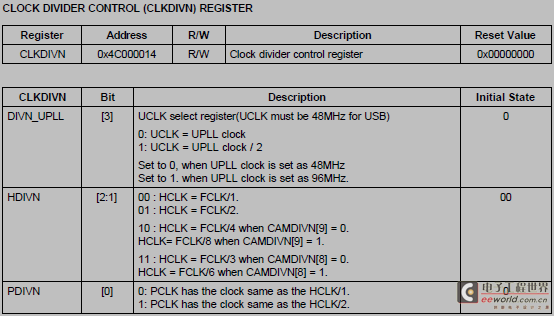

从上图可以看出,我们只需要设置MPLLCON寄存器就可以确定FCLK了,再通过CLKdivN寄存器我们就可以设置FCLK、HCLK、PCLK三者之间的比例了。

前面说过,MPLL启动后需要等待一段时间(Lock Time),使得其输出稳定。位[31:16]用于UPLL,位[15:0]用于MPLL。使用确省值0x00ffffff即可。

S3C2440时钟系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)