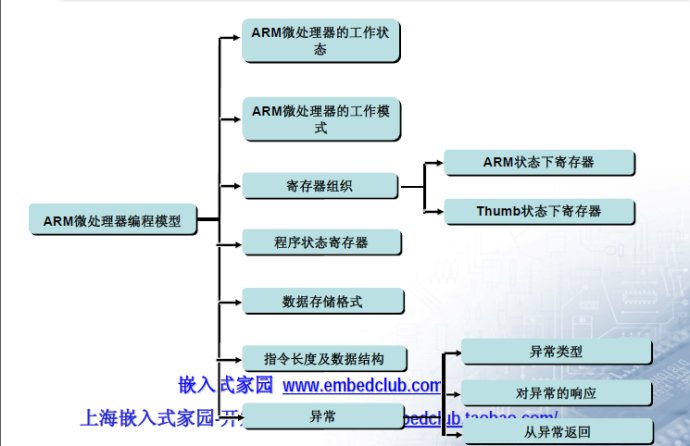

ARM·微处理器的编程模型

了解ARM的结构特点

了解ARM的编程的工作模式

了解ARM的内部资源

了解ARM的异常处理机制

ARM9处理器内核使用VT4版本的ARM结构,具有两种操作状态

1)ARM状态:32位,执行的是字方式的ARM指令 ;

2)Thumb状态:16位,执行的是半字方式的Thumb指令;

(ARM和Thumb状态都是在执行程序,只不过命令的长度不一样,类似于跑跑卡丁车的氮气状态和普通状态)

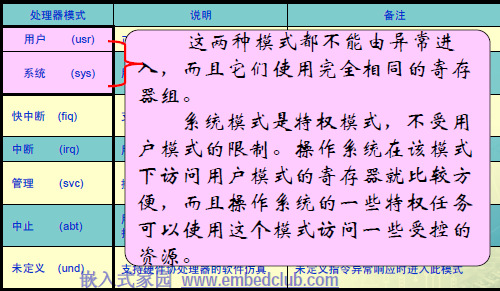

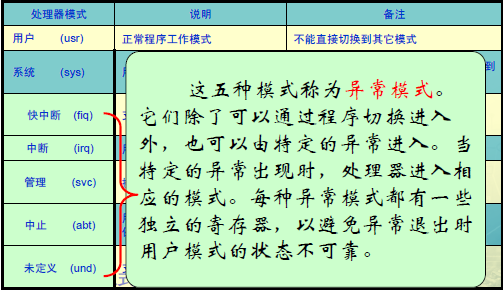

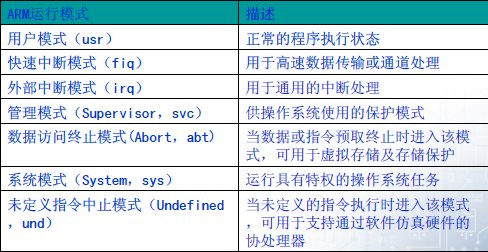

1) 用户和系统模式 ;

(感觉类似于linux中的普通用户和超级用户)

2)异常模式

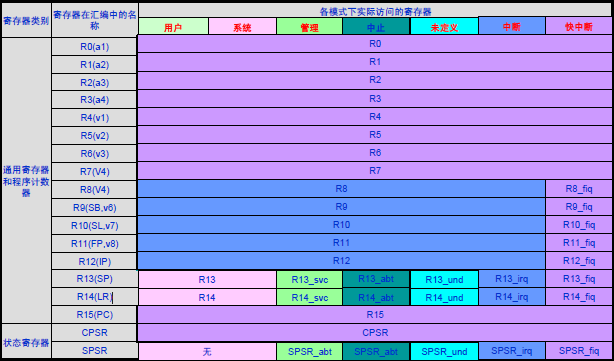

3)ARM9处理器支持的7种寄存器工作模式

(ARM9有7种工作模式,分别对应7种不同的寄存器组合(内部37个寄存器的组合))

1)通用寄存器

(31个32位通用寄存器和6个状态寄存器(类似于单片机))

R0-R12为保存数据或地址的通用寄存器,不用被体系和结构作为特殊的用途 ;

(R0-R7为未分组的寄存器:对于任何处理器模式都可以使用;

(R8-R12:有两个分组物理寄存器,提供了一个专门给FIQ模式的寄存器,这样才可以加速FIQ处理速度)

R13:堆栈指针(SP);ARM指令集中没有特殊的R13指令;Thumb中存在R13的指令

R14:链接寄存器(LR),在结构上有2个特殊功能(1.模式自身的R14用于保存子程序返回地址,2发生异常用于保存异常返回地址)

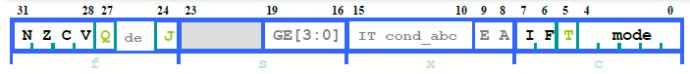

2)程序状态寄存器(CPSR)

·mode:表示处理器的工作状态

·T:0,ARM state;1,Thumb state ;

·interrupt disable bits

I=1:Disables the IRQ

F=1:Disable the FIO

·condition code flags

N = Negative result from ALU (非零)

Z = Zero result from ALU (结果是零)

C = ALU operation Carried out (进位)

V = ALU operation Overflowed

v5,v6的

Q:dsp扩展单元

J:java加速器

(处理器用于存储数据方式有两种,分为大字节序和小字节序

大字节序:高字节在低位,低字节在高位

小字节序:高字节在高位,低字节在低位

*老版本只支持小字字节,现在都支持,linux网络编程采用大字节序)

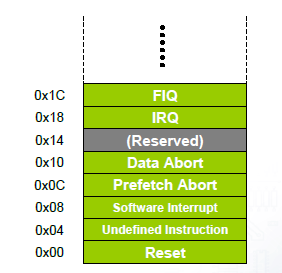

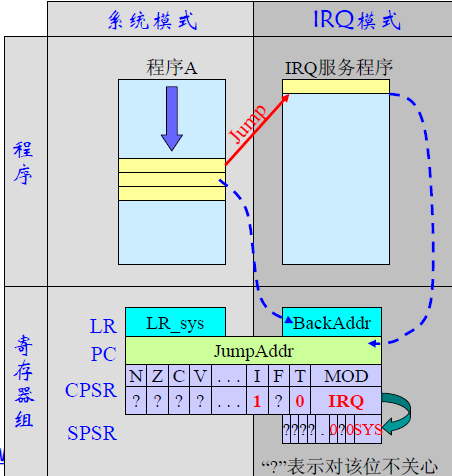

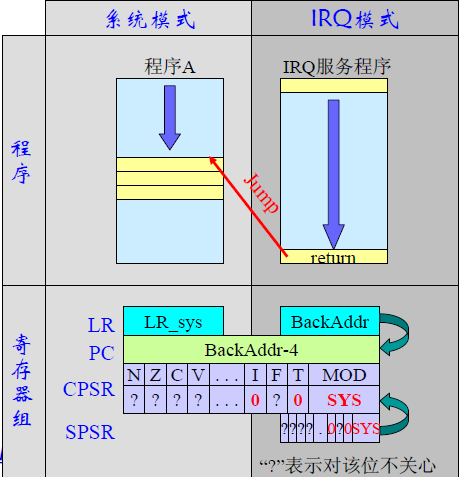

(只要正常的程序流被暂时中止,处理器将进入异常模式。在处理异常之前,ARM9内核保存的当前的处理器状态(CPSR->SPSR),这样当处理器结束时可以恢复执行原来的程序(SPSR->CPSR))

Reset:复位中断 ;

Undefineed Instruction :未定义指令;

Software Interrupt:软件中断

Prefetch Abort:预取指令中止 ;

Date Abort :数据中止 ;

IRQ:外部中断 ;

FIQ:快速中断请求 ;

1)进入异常:

*LR中保存当前执行指令的下一条指令的地址:LR=PC-4

*CPSR->SPSR (保留状态)

*CPSR->与异常类型相对应的状态

*PC从相关异常向量处取址

*跳转,执行命令

2)从异常返回

*SPSR->CPSR

*LR寄存值减去一个偏移量后复制到PC寄存器,跳转被中断的用户程序

(这里,结合ARM7的3级流水线处理结构可以详细的思考一下,但是为什么第一步不把PC-8保存在R14里面?)

ARM微处理器编程模 相关文章:

- ARM应用系统开发详解 第2章 ARM微处理器的编程模型(11-20)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)