飞思卡尔HCS12中断

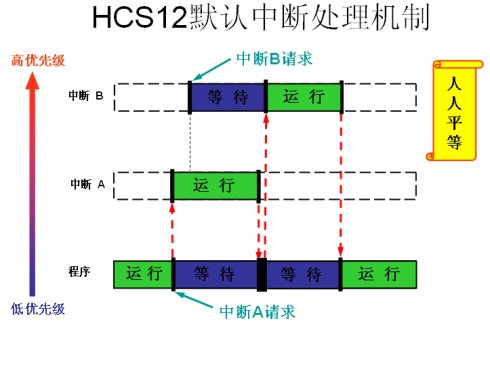

在进入中断服务程序时,I位自动置1,禁止其他可屏蔽中断

即使有优先级更高的中断请求,也必须等当前中断服务程序执行完以后才能响应

优先级的作用只有在多个中断源同时请求中断时在能体现

无法实现中断嵌套

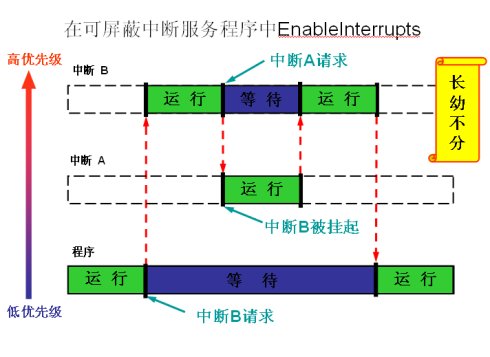

如果在进入中断服务程序时,手动对I位清零:

任何其他可屏蔽中断都可以被响应,无论其优先级有多高

中断响应由时间控制,可以实现中断嵌套

对中断执行无法预测

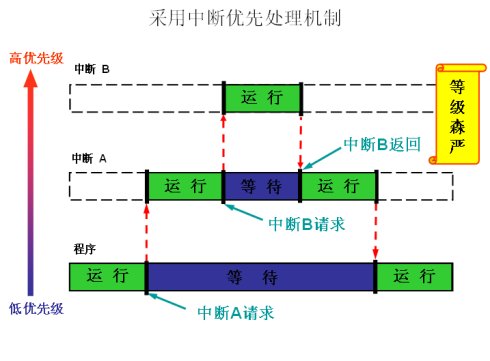

HPRIO寄存器

写入HPRIO中的中断向量的后八位,可以改变该中断的优先级

同样,优先级的作用只有在多个中断源同时请求中断时在能体现

1:在中断服务程序中,首先对I为清零,即EnableInterrupts

2:选择优先级更高的中断源可以进入响应中断

3:设置优先等级

一个中断源为低优先级,其他为高优先级

在低优先级中断服务程序中,对I位清零

在高优先级中断服务程序中,不清零

(二)多级

利用局部的中断屏蔽位

比如Timer Channel0 的中断屏蔽位

例如:

--中断向量地址 $FFF0 – FFF1 为低优先级

--其他的中断为高优先级

--在$FFF0 – FFF1 中断服务程序中,EnableInterrupts(I位清零)

--其他的中断包括自己都可以在中断服务程序执行时,被响应

--在其他的中断服务程序中,I位不清零(默认)

--只有当前中断服务程序执行完后,才能响应其他的中断请求

自定义优先级 | 中断向量地址 | 中断源 | CCR屏蔽位 | 局部屏蔽位 | HPRIO |

1 中 | $FFEE,$FFEF | ECT通道0 | I | TIE_C0I | $EE |

0 低 | $FFEC,$FFED | ECT通道1 | I | TIE_C1I | $EC |

2 高 | $FFEA,$FFEB | ECT通道2 | I | TIE_C2I | $EA |

要求:

HPRIO = 0xEA:ECT0,1,2同时请求中断时,CPU将会首先响应通道2

默认时,CPU将会首先响应通道0

优先机制-多级

情况 1:

每个中断都单独发生,在一个中断程序执行时,没有其他中断

情况 2:

在执行ECT1的中断服务程序时,ECT0请求中断

ECT0中断服务程序将被执行

情况 3:

在执行ECT2的中断服务程序时,ECT0请求中断

ECT2的中断服务程序执行结束后,执行ECT0的中断服务程序

情况 4:

ECT1,ECT2同时请求中断

ECT1的中断服务程序先执行,当EnableInterrupts后

执行ECT2的中断服务程序

ECT2的中断服务程序执行结束后,返回执行ECT1的中断服务程序

TIE_C1I = 0; //关闭ECT1局部中断

TIE_C2I = 1; //开放ECT2局部中断

EnableInterrupts; //开放全局中断

…

TIE_C1I = 1; //开放ECT1局部中断

TIE_C2I = 1; //开放ECT2局部中断

在ECT1中断服务程序中(自定义优先级最低):

TIE_C0I = 1;

TIE_C2I = 1;

EnableInterrupts; //开放全局中断

…

TIE_C0I = 1;

TIE_C2I = 1;

在ECT2中断服务程序中(自定义优先级最高):

用户程序

飞思卡尔HCS12中 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)