上拉电阻和下拉电阻的选择

这个提法基本是对的,但也不全对。下面详细加以说明。

管脚上拉下拉电阻设计出发点有两个:

一个是在正常工作或单一故障状态下,管脚均不应出现不定状态,如接头脱落后导致的管脚悬空;

二是从功耗的角度考虑,就是在长时间的管脚等待状态下,管脚端口的电阻上不应消耗太多电流,尤其是对电池供电设备。

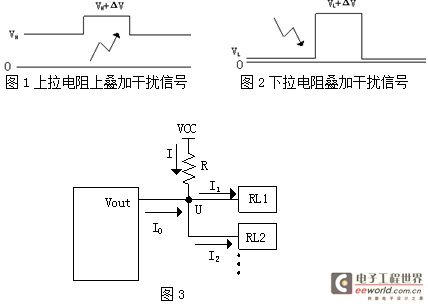

从抗扰的角度,信号端口优选上拉电阻。上拉电阻时,在待机状态下,源端输入常为高阻态,如果没有上拉电阻或下拉电阻,输入导线呈现天线效应,一旦管脚受到辐射干扰,管脚输入状态极容易被感应发生变化。所以,这个电阻是肯定要加的。下一个问题就是加上拉还是下拉。

如果加了下拉,在平常状态下,输入表现为低电平,但辐射干扰进来后,会通过下拉电阻泻放到地,就会发生从Low—High的一个跳变,产生误触发。相当于一个乞丐,你给了他10万元,他的生活方式就会从穷人到富人发生一个改变。

但如果加了上拉电阻,在平常状态下,输入表现为高电平,辐射干扰进来后,如果低也没关系,上拉电阻会将输入端钳位在高电平,如果辐射干扰强,超过了Vcc的电平,导线上的高电平干扰会通过上拉电阻泻放到Vcc上去,无论怎样干扰,都只会发生High—Higher的变化,不会产生误触发。相当于人家本来是一个富豪,你给了他10万元,他的生活方式不会发生任何的改变。

A、当I0>= I1+ I2

B、当I0< I1+ I2

以上三式可以得出:R>=(VCC- VLmax)/I’

上拉电阻下拉电 相关文章:

- 上拉电阻与下拉电阻的作用和区别(11-28)

- 单片机上拉电阻、下拉电阻详解(11-18)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)