TQ2440国嵌学院gboot-时钟初始化

1:设置lock time寄存器

2:设置分频系数(FCLK:HCLK:PCLK)

3:设定CPU到异步模式(通常FCLK不等于HCLK)

4:设置FCLK

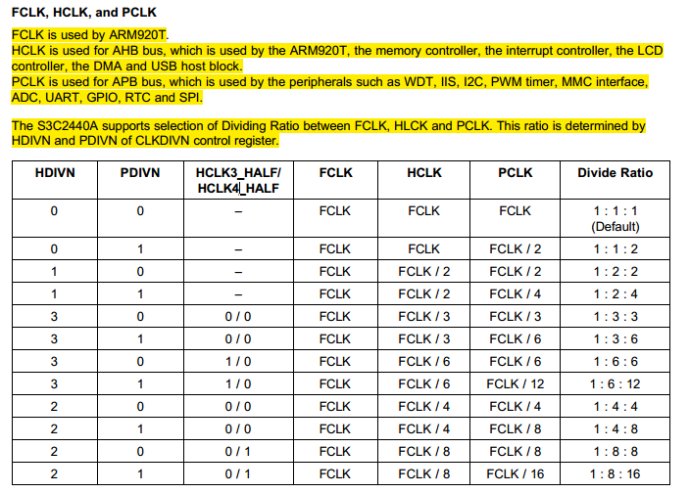

首先了解下CPU的时钟分类:

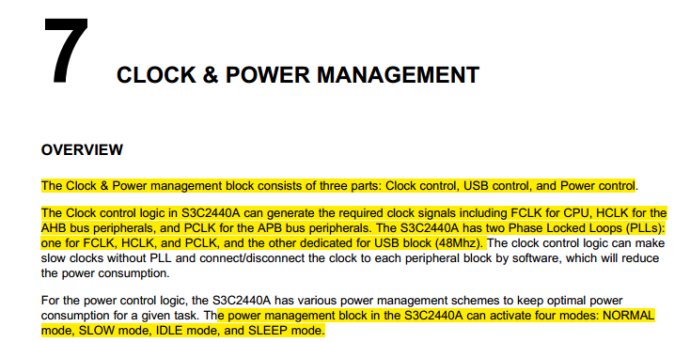

同样在S3C2440中找到CLOCK第7章这一章如下:

从上面的文字中,可以得到FCLK主要是CPU核的工作时钟,HCLK是AHB总线(LCD,DMA)的工作时钟,PCLK是APB总线(UART,GPIO)工作时钟。

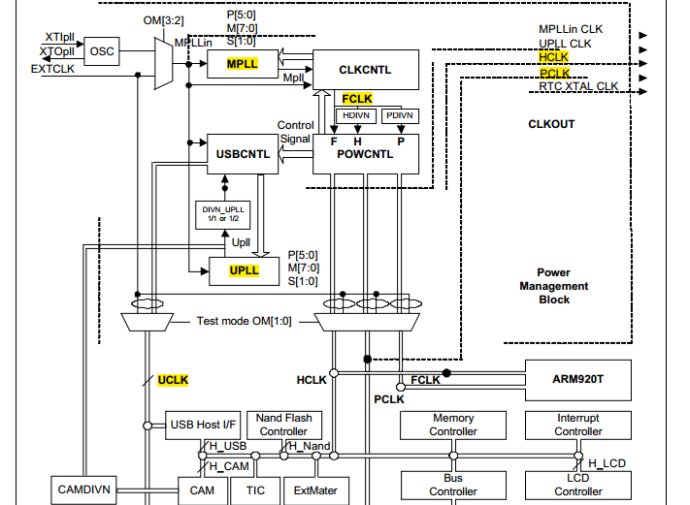

下面是CPU内部时钟电路结构图

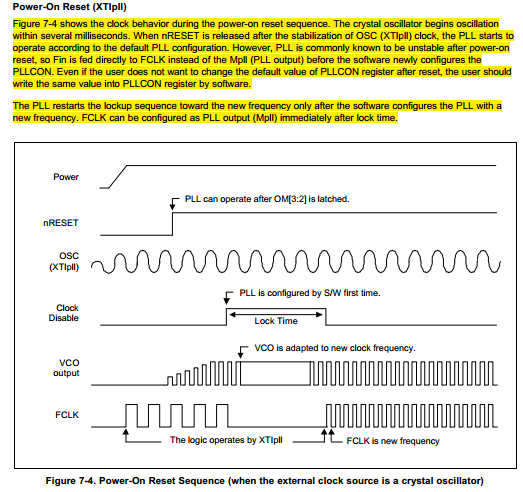

其次是CPU的启动时钟时序:

从上图可以看出,在上电后,nRESET会拉高,clock开始起振输出时钟信号,此时CPU工作在12MHz,然后PLL开始进入软体设置,这时候FCLK为0,没有时钟信号供CPU工作,当然时间很短,当PLL设定后FCLK以新的时钟频率供CPU工作。

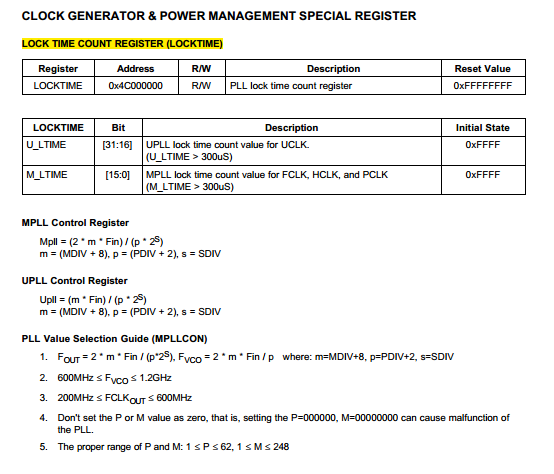

LOCK TIME寄存器设定:

通常情况下不设定,采用默认值。

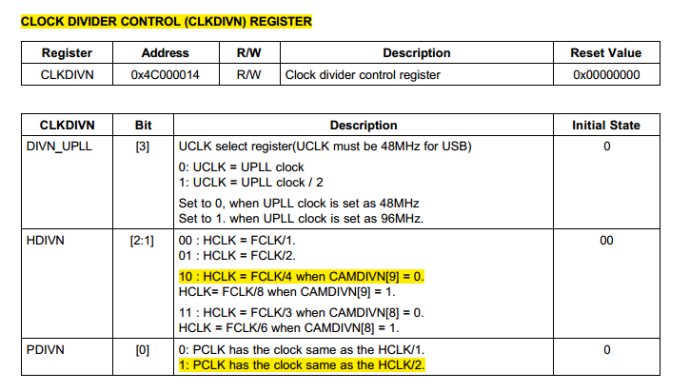

再次如何设定分频系数呢?如下图

通过选择HdivN

因此设定HdivN=2,也就是01;设定PdivN=1,也就是0。divN_UPLL不设定,组合起来也就是在CKdivN寄存器里写入0X5(0b000101),寄存器的地址是0x4c000014。

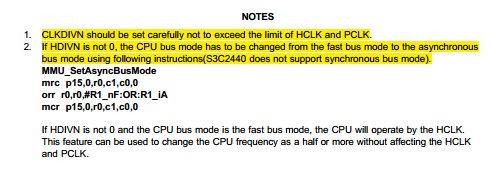

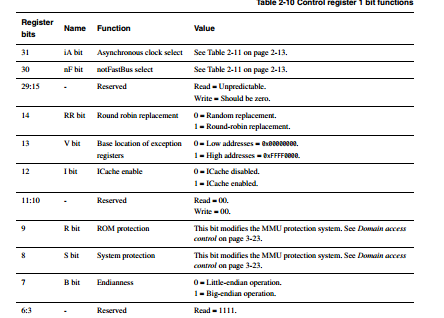

如何设定CPU到异步模式呢?

为什么要设定CPU到异步模式呢?看下面介绍:

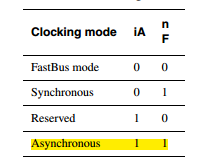

翻译可知,当HdivN不等于0的时候,要设定CPU到异步模式,HdivN不等于0代表什么呢?首先看等于0,等于0代表FCLK=HCLK,也就是CPU核工作时钟等于总线时钟,当2者相同的时候是同步,不相等就是异步模式。因此要设定到异步模式。如何设置到异步模式?

代码上面也有给出,通过设定CP15的C1寄存器的nF和iA位都为1即可。

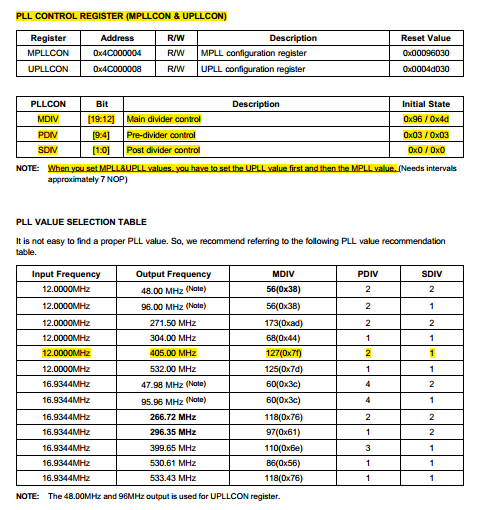

最后来看设定FCLK的频率:

首先我们采用的CPU的工作频率是405MHZ,也就是Mdiv=0X7F,Pdiv=10;Sdiv=1

全部代码:

#define CLKdivN 0x4c000014

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<12)|(2<4)|(1<0))

init_clock:

TQ2440国嵌学院gboot时钟初始 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)