GNU ARM汇编--(七)s3c2440的串口控制

UART clock / ( buad rate x 16) ) –1

( UART clock: PCLK, FCLK/n or UEXTCLK )

接下来看各个寄存器的描述:

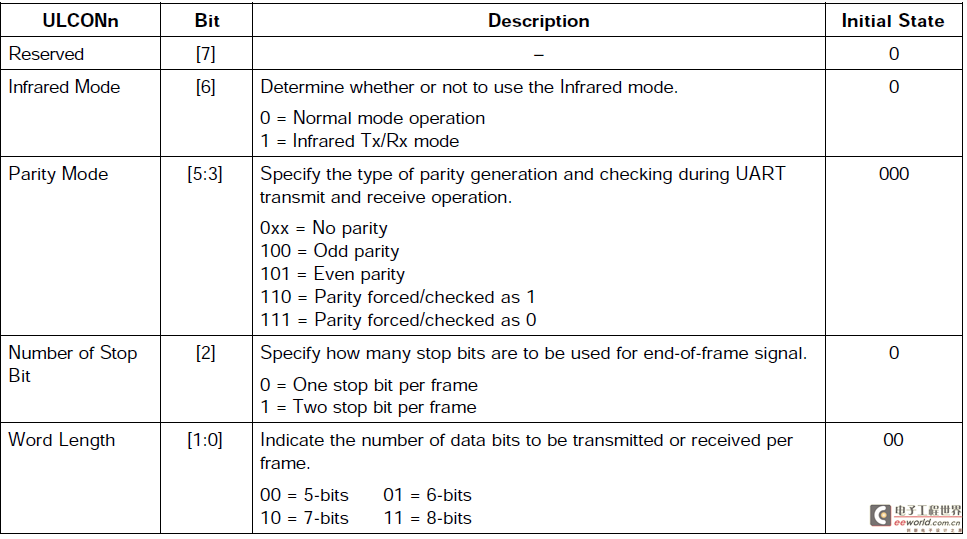

UART LINE CONTROL REGISTER

ULCONn用来配置每一帧数据的格式的:

根据上图,配置如下:

IR mode[6] = 0(普通模式) Parity Mode[5:3] = 0xx(无校验) Number of Stop Bit[2] = 0(一个停止位)

word Length[1:0] = 11(8-bits)

UART CONTROL REGISTER

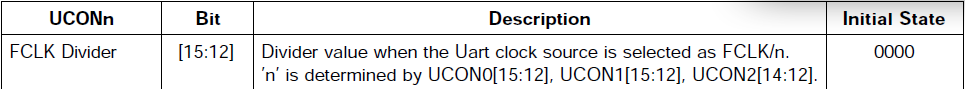

如果Uart的时钟源用FCLK/n,那么FCLK Divider就是配置这个n的

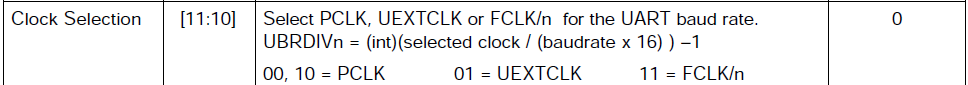

这个地方就是配置Uart的时钟源

Tx Interrupt Type [9] 中断请求类型:0是Pulse 1是Level

Rx Interrupt Type [8] 中断请求类型:0是Pulse 1是Level

Rx Time Out Enable [7] 在FIFO使能的情况下,是否打开Rx Time Out中断 0是关闭 1是打开

Rx Error Status Interrupt Enable [6] 使能Uart对异常产生中断,比如各种错误 0是关闭 1是打开

Loopback Mode [5] 回环模式 0是普通模式 1是回环模式

Send Break Signal [4] 是否发送终止信号 0是正常 1是发送终止信号

Transmit Mode [3:2] 决定使用哪种功能来写数据到发送缓冲寄存器 01中断请求或轮循模式

Receive Mode [3:2] 决定使用哪种功能来从接收缓冲寄存器读数据 01中断请求或轮循模式

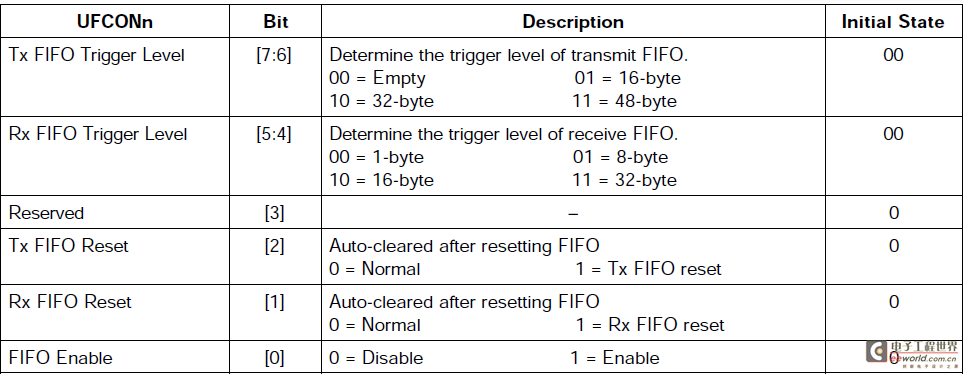

UART FIFO CONTROL REGISTER

UART MODEM CONTROL REGISTER

这个和MODEM控制相关,设置为默认值就行.

UART TX/RX STATUS REGISTER

这个寄存器是只读的,负责反映发送接收的状态

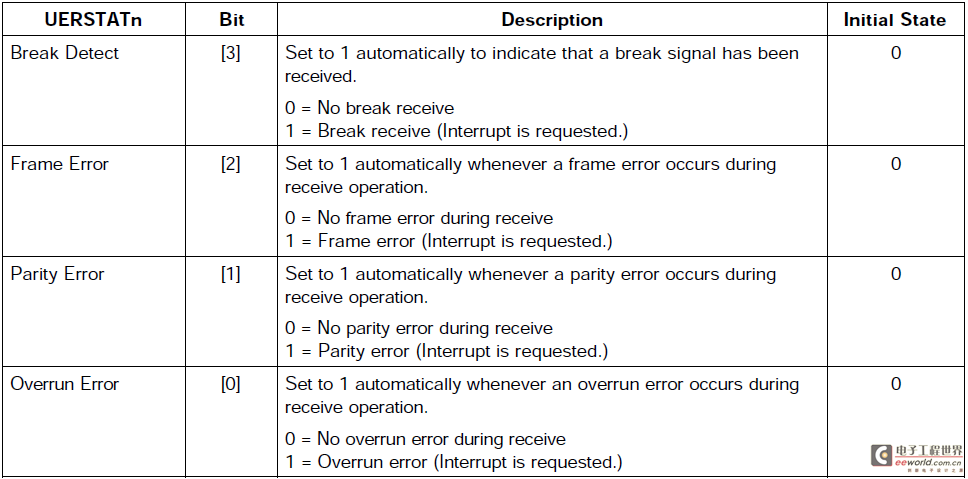

UART ERROR STATUS REGISTER

这个寄存器也是只读的,负责反映错误状态

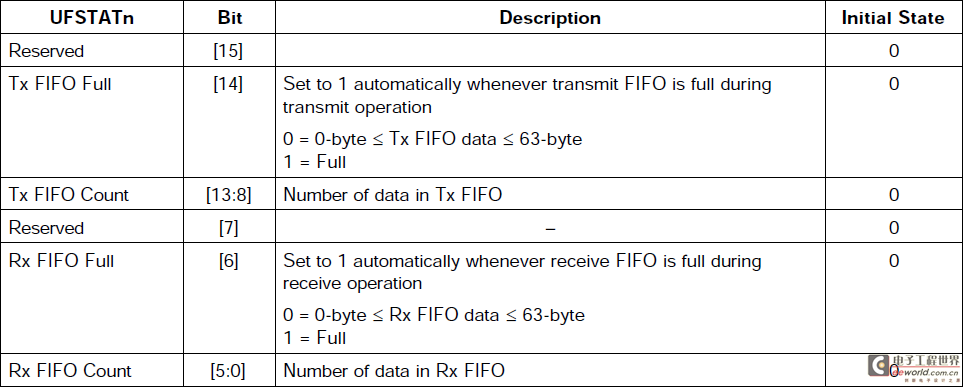

UART FIFO STATUS REGISTER

这个寄存器也是只读的,负责反映FIFO的状态

UART MODEM STATUS REGISTER

这个寄存器是MODEM状态的,不用管它

UART TRANSMIT BUFFER REGISTER (HOLDING REGISTER & FIFO REGISTER)

发送缓冲寄存器:FIFO模式下叫FIFO寄存器,非FIFO模式下叫Holding寄存器

需要注意的就是大小端

UART RECEIVE BUFFER REGISTER (HOLDING REGISTER & FIFO REGISTER)

接收缓冲寄存器:FIFO模式下叫FIFO寄存器,非FIFO模式下叫Holding寄存器

UART BAUD RATE divISOR REGISTER

波特率除数寄存器

UBRdivn = (int)( UART clock / ( buad rate x 16) ) –1

( UART clock: PCLK, FCLK/n or UEXTCLK )

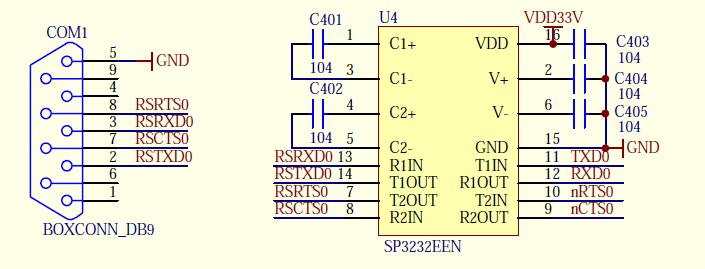

看完datasheet后,我们看一下TQ2440的原理图:

由原理图可以看出,TQ2440使用的UART0,我们用MAX232芯片做电平转换.

有了datasheet和原理图,下面就开始写汇编代码了:

时钟初始化和uart初始化用汇编写的:

[cpp]view plaincopy

- @.externuart_test

- .equGPBCON,0x56000010

- .equGPBDAT,0x56000014

- .equGPB5_out,(1<(5*2))

- .equGPB6_out,(1<(6*2))

- .equGPB7_out,(1<(7*2))

- .equGPB8_out,(1<(8*2))

- .equGPHCON,0x56000070

- .equGPHDAT,0x56000074

- .equGPBVALUE,(GPB5_out|GPB6_out|GPB7_out|GPB8_out)

- .equLOCKTIME,0x4c000000

- .equMPLLCON,0x4c000004

- .equUPLLCON,0x4c000008

- .equM_Mdiv,92

- .equM_Pdiv,1

- .equM_Sdiv,1

- .equU_Mdiv,56

- .equU_Pdiv,2

- .equU_Sdiv,2

- .equCLKdivN,0x4c000014

- .equdivN_UPLL,0

- .equHdivN,1

- .equPdivN,1@FCLK:HCLK:PCLK=1:2:4

- .equULCON0,0x50000000

- .equIR_MODE,0x0@[6]正常模式

- .equParity_Mode,0x0@[5:3]无校验位

- .equNum_of_stop_bit,0x0@[2]一个停止位

- .equWord_length,0b11@[1:0]8个数据位

- .equUCON0,0x50000004

- .equFCLK_Div,0@[15:12]时钟源选择用PCLK,所以这里用默认值

- .equClk_select,0b00@[11:10]时钟源选择使用PCLK

- .equTx_Int_Type,1@[9]中断请求类型为Level

- .equRx_Int_Type,0@1@[8]中断请求类型为Level

- .equRx_Timeout,0@[7]

- .equRx_Error_Stat_Int,1@[6]

- .equLoopback_Mode,0@[5]正常模式

- .equBreak_Sig,0@[4]不发送终止信号

- .equTx_Mode,0b01@[3:2]中断请求或轮循模式

- .equRx_Mode,0b01@[1:0]中断请求或轮循模式

- .equUFCON0,0x50000008

- .equTx_FIFO_Trig_Level,0b00@[7:6]

- .equRx_FIFO_Trig_Level,0b00@[5:4]

- .equTx_FIFO_Reset,0b0@[2]

- .equRx_FIFO_Reset,0b0@[1]

- .equFIFO_Enable,0b0@[0]非FIFO模式

- .equUMCON0,0x5000000C@这个寄存器可以不管的

- .equUTRSTAT0,0x50000010

- .equUERSTAT0,0x50000014

- .equUFSTAT0,0x50000018

- .equUMSTAT0,0x5000001C

- .equUTXH0,0x50000020@(L小端)

- .equURXH0,0x50000024@(L小端)

- .equUBRdiv0,0x50000028

- .equUBRdiv,0x35@PCLK=400M/4=100MUBRdiv=(int)(100M/115200/16)-1=53=0x35

- .global_main

- _main:

- ldrr0,=GPBCON

- ldrr1,=0x15400

- strr1,[r0]

- ldrr2

ARM汇编s3c2440串口控 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)