S3C2440时钟设置详解

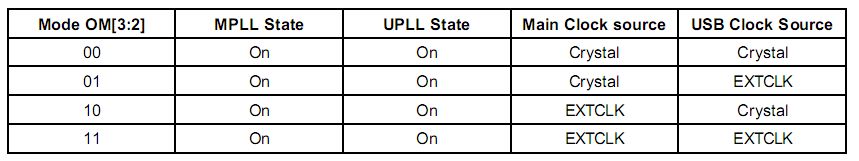

S3C2440A的主时钟源由外部时钟(EXTCLK)或者外部晶振(XTIPll)提供,输入时钟源由模式控制引脚OM3和OM2控制选择,在复位信号的上升沿参考OM3和OM2的引脚将OM[3:2]的状态在内部锁定,如图1所示

图1 引导启动时的时钟源选择

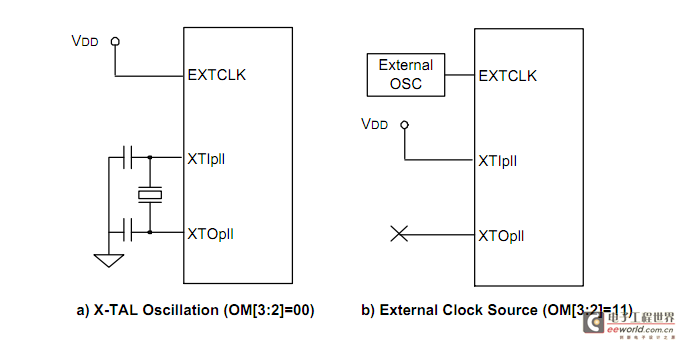

选择不同输入时钟源时连接方式如图2所示:

图2 时钟连接参考

通过在片内集成的2个锁相环:MPLL和UPLL,可对输入的Fin=12MHz的晶振频率进行倍频。S3C2440使用了三个倍频因子Mdiv、Pdiv和Sdiv来设置倍频,通过寄存器MPLLCON和UPLLCON可设置倍频因子。其中MPLLCON寄存器用于设置处理器内核时钟主频FCLK,其输入输出频率间的关系为

FCLK=MPLL=(2*m*Fin)/(p*2^s)

其中m=(Mdiv+8), p=(Pdiv+2), s=Sdiv。

其中UPLLCON寄存器用于产生48MHz或96MHz,提供USB时钟(UCLK),其输入输出频率间的关系为

UCLK=UPLL=(m * Fin) / (p * 2^s)

其中m=(Mdiv+8), p=(Pdiv+2), s=Sdiv。

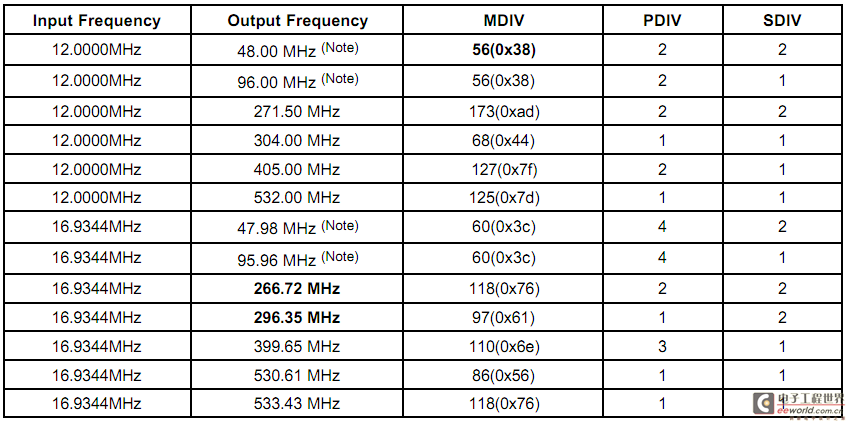

手工计算相对复杂些,我们可以根据欲得到的主频FCLK大小,直接通过查表来获知各倍频因子的设置参数,详见。

S3C2440的数据手册中提供了一个表格来查询各个输出频率和输入频率所对应的MPLL中参数m、p和s的值,使用的时候最好只使用该表格中推荐的数值。

图3 PLL真值表

通过图3的真值表,我们可以得到如果输入时钟为12MHz,输出时钟FCLK为405MHz,可以选择Mdiv为127,Pdiv为2,Sdiv为1。输出48MHz和96MHz是UPLLCON使用的。

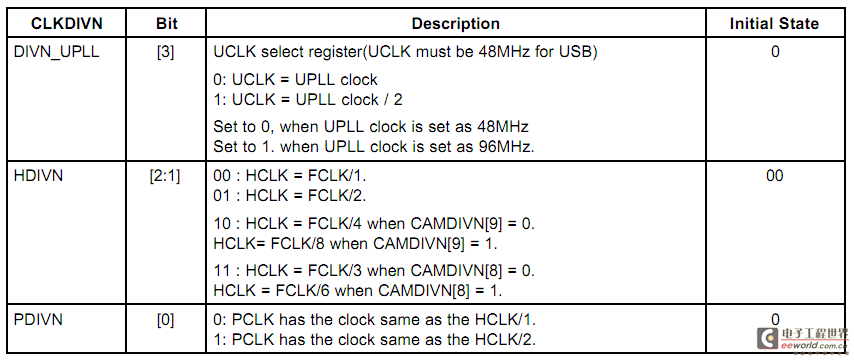

除了可设置内核时钟FCLK,还需要设置AHB总线设备使用的HCLK和APB总线设备使用的PCLK。通过CLKdivN和CAMdivN这两个寄存器可设置三者的分频关系,如图4 为CLKdivN的说明,可以通过设置CLKdivN和CAMdivN的相关位来设置这三个时钟。

图4 FCLK、HCLK和PCLK关系

具体可参观数据手册中对此的说明。即若主频FLCK是400MHz,如果按照1:4:8的设置,可以先设置CLKdivN为0101,然后设置CAMdivN的第9位为0(不设置的时候该位默认为0),此时HLCK是100MHz,PLCK是50MHz。

可将该频率映射到CLKOUT0引脚,对其测试验证。

在我们搭建好2440的硬件平台后,我们在调试硬件的时候,通常需要将系统的时钟测试引脚引出来测试,以确认系统是否达到设计的要求。2440提供了CLKOUT0和CLKOUT1这两个引脚用于测试时钟。可以通过设置MISCCR寄存器的CLKSEL0和CLKSEL1位来选择CLKOUT0和CLKOUT1的时钟源。其时钟源分别有000=MPLL输出,001为UPLL输出,010为RTC输出,011为HCLK,100为PCLK,101为DCLK1/0,11X为保留的。

测试用的汇编程序如下:

AREA Example,CODE,READONLY;声明代码段Example

ENTRY ;标示程序入口

CODE32 ;声明32位ARM指令

START LDR R0, =0x0005C011 ;FCLK=400MHz

LDR R1, =0x4C000004 ;MPLLCON寄存器

STR R0,[R1]

LDR R0, =0x00000005 ;FCLK:HCLK:PCLK=1:4:8

LDR R1, =0x4C000014 ;CLOCK divIDER control

STR R0,[R1]

LDR R0, =(0xa<18)

LDR R1, =0x56000070 ;端口H控制寄存器

STR R0,[R1]

;CLKOUT0、CLKOUT1引脚复用(选择GPH10-9的功能为CLKOUT0和1)

LDR R0, =(0x86<3)

;CLKOUT0和CLKOUT1分别输出HCLK及PCLK

LDR R1, =0x56000080 ;MISCCR寄存器

STR R0,[R1]

END

测试没错的话就Okay了

S3C2440时钟设 相关文章:

- 关于S3C2440时钟设置的理解(11-11)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)