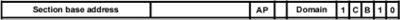

上图是描述符的结构

Section base address:段基地址(相当于页框号首地址)

AP:访问控制位Access Permission

Domain:访问控制寄存器的索引。Domain与AP配合使用,对访问权限进行检查

C:当C被置1时为write-through (WT)模式

B:当B被置1时为write-back (WB)模式(C,B两个位在同一时刻只能有一个被置1)

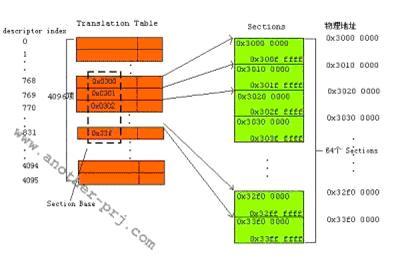

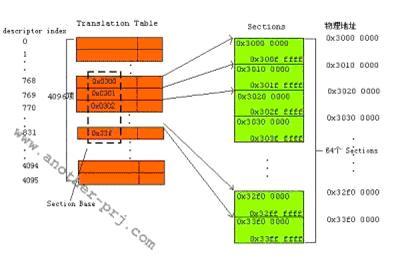

下面是s3c2410内存映射后的一个示意图:

我的s3c2410上配置的SDRSAM大小为64M,该SDRAM的物理地址范围是0x3000 0000~0x33FF FFFF(属于Bank 6),由于1个Section的大小是1M,所以该物理空间可以被分成64个物理段(页框).

在Section模式下,送进MMU的虚拟地址(注1)被分为两部分(这点和我们上面举的例子是一样的),这两部分为Descriptor Index(相当于上面例子的Page Index)和Offset,descript index长度为12bit(2^12=4096,从这个关系式你能看出什么?:) ),Offset长度为20bit(2^20=1M,你又能看出什么?:)).观察一下一个描述符(Descriptor)中的Section Base Address部分,它长度为12 bit,里面的值是该虚拟段(页)映射成的物理段(页框)的物理地址前12bit,由于每一个物理段的长度都是1M,所以物理段首地址的后20bit总是为0x00000(每个Section都是以1M对齐),确定一个物理地址的方法是物理页框基地址+虚拟地址中的偏移部分=Section Base Address<20+Offset,呵呵,可能你有点糊涂了,还是举一个实际例子说明吧。

假设现在执行指令MOV REG, 0x30000012,虚拟地址的二进制码为00110000 00000000 00000000 00010010,前12位是Descriptor Index= 00110000 0000=768,故在Translation Table里面找到第768号描述符,该描述的Section Base Address="0x0300",也就是说描述符所描述的虚拟段(页)所映射的物理段(页框)的首地址为0x3000 0000(物理段(页框)的基地址=Section Base Address左移20bit=0x0300<20=0x3000 0000),而Offset=000000 00000000 00010010=0x12,故虚拟地址0x30000012映射成的物理地址=0x3000 0000+0x12=0x3000 0012(物理页框基地址+虚拟地址中的偏移)。你可能会问怎么这个虚拟地址和映射后的物理地址一样?这是由我们定义的映射规则所决定的。在这个例子中我们定义的映射规则是把虚拟地址映射成和他相等的物理地址。我们这样书写映射关系的代码:

void mem_mapping_linear(void)

{

unsigned long descriptor_index, section_base, sdram_base, sdram_size;

sdram_base=0x30000000;

sdram_size=0x 4000000;

for (section _base= sdram_base,descriptor_index = section _base>>20;

section _base < sdram_base+ sdram_size;

descriptor_index+=1;section _base +=0x100000)

{

*(mmu_tlb_base + (descriptor_index)) = (section _base>>20) | MMU_OTHER_SECDESC;

}

}

上面的这段段代码把虚拟空间0x3000 0000~0x33FF FFFF映射到物理空间0x3000 0000~0x33FF FFFF,由于虚拟空间与物理空间空间相吻合,所以虚拟地址与他们各自对应的物理地址在值上是一致的。当初始完Translation Table之后,记得要把Translation Table的首地址(第0号描述符的地址)加载进协处理器CP15的Control Register2(2号控制寄存器)中,该控制寄存器的名称叫做Translation table base (TTB) register。

以上讨论的是descriptor中的Section Base Address以及虚拟地址和物理地址的映射关系,然而MMU还有一个重要的功能,那就是访问控制机制(Access Permission )。

简单说访问控制机制就是CPU通过某种方法判断当前程序对内存的访问是否合法(是否有权限对该内存进行访问),如果当前的程序并没有权限对即将访问的内存区域进行操作,则CPU将引发一个异常,s3c2410称该异常为Permission fault,x86架构则把这种异常称之为通用保护异常(General Protection),什么情况会引起Permission fault呢?比如处于User级别的程序要对一个System级别的内存区域进行写操作,这种操作是越权的,应该引起一个Permission fault,搞过x86架构的朋友应该听过保护模式(Protection Mode),保护模式就是基于这种思想进行工作的,于是我们也可以这么说:s3c2410的访问控制机制其实就是一种保护机制。那s3c2410的访问控制机制到底是由什么元素去参与完成的呢?它们间是怎么协调工作的呢?这些元素总共有:

1.协处理器CP15中Control Register3:DOMAIN ACCESS CONTROL REGISTER

2.段描述符中的AP位和Domain位

3.协处理器CP15中Control Register1(控制寄存器1)中的S bit和R bit

4.协处理器CP15中Control Register5(控制寄存器5)

5.协处理器CP15中Control Register6(控制寄存器6)

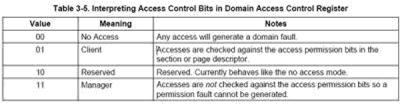

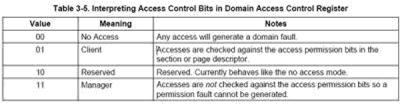

DOMAIN ACCESS CONTROL REGISTER是访问控制寄存器,该寄存器有效位为32,被分成16个区域,每个区域由两个位组成,他们说明了当前内存的访问权限检查的级别,如下图所示:

每区域可以填写的值有4个,分别为00,01,10,11(二进制),他们的意义如下所示:

00:当前级别下,该内存区域不允许被访问,任何的访问都会引起一个domain fault

01:当前级别下,该内存区域的访问必须配合该内存区域的段描述符中AP位进行权检查

10:保留状态(我们最好不要填写该值,以免引起不能确定的问题)

11:当前级别下,对该内存区域的访问都不进行权限检查。

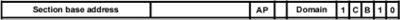

我们再来看看discriptor中的Domain区域,该区域总共有4个bit,里面的值是对DOMAIN ACCESS CONTROL REGISTER中16个区域的索引.而AP位配合S bit和A bit对当前描述符描述的内存区域被访问权限的说明,他们的配合关系如下图所示: