飞思卡尔初学之PWM调试笔记

本文着重应用实践,理论性的东西少谈为妙,因为理论的东西资料上都有。想借此平台记录下调试心得以免日后遗忘,因本人也是初学该款单片机,难免有错误之处,还希望达人指点。

PWM应用步骤:

一、PLL初始化,这一步应该说不算PWM设置的内容,但是又必须设置,因为这关系着PWM周期值的计算。

void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

{ //锁相环时钟=2*16*(2+1)/(1+1)=48MHz

CLKSEL=0X00;

PLLCTL=0XE1;

REFDV = 1; //总线时钟=48/2=24MHz

SYNR = 2;

_asm(nop); // BUS CLOCK=24M

_asm(nop);

while (!(CRGFLG & 0x08)) ;

CLKSEL = 0x80; //选定锁相环时钟

}

用了这个PLL初始化函数以后,总线时钟就是24M了。

二、PWM相关设置

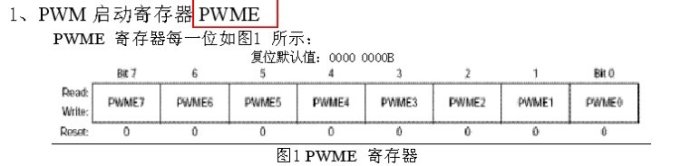

1、禁止PWM。PWME

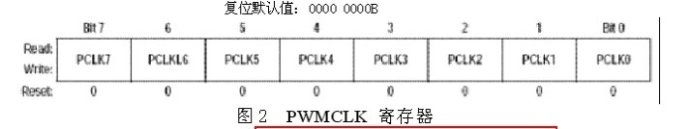

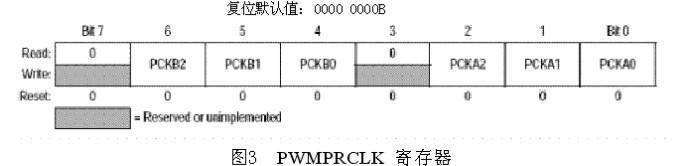

2、选择时钟源。PWMPRCLK, PWMSCLA, PWMSCLB ,PWMCLK。 其中通道0 、1、4、5 可以选择 ClockA ClockSA。通道2、3、6、7 可以选择ClockB ClockSB

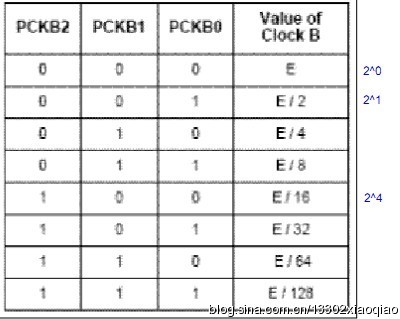

其中值得说明的是ClockA或ClockB是通过总线时钟预分频获得的。ClockSA或ClockB是分别对ClockA ClockB再次进行分频获得的。分频系数的设置都有相应的寄存器进行设置。后面会提到。

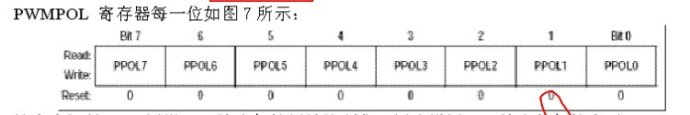

3、极性设置 PWMPOL 。极性是指初始时通道输出的是高电平还是低电平。这个是关系到占空比的计算。

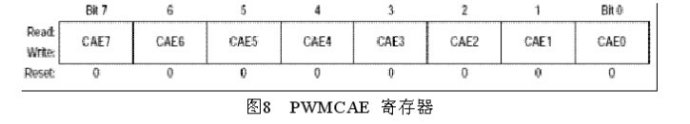

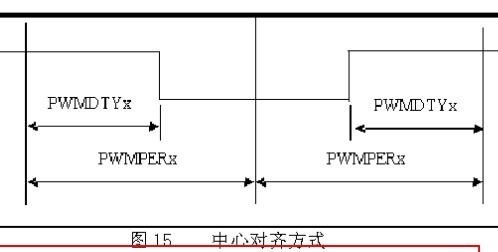

4、选择对齐方式 PWMCAE。对齐方式有左对齐和中间对齐两种。两种方法在计算占空比时也有差别。

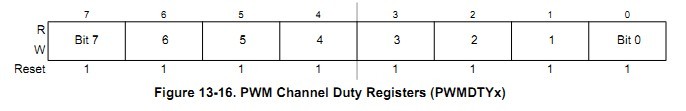

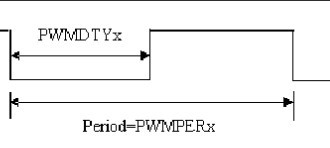

5、设置周期和占空比。PWMPERx PWMDTYx.

6、使能PWM。PWME。

相关寄存器列表如下。

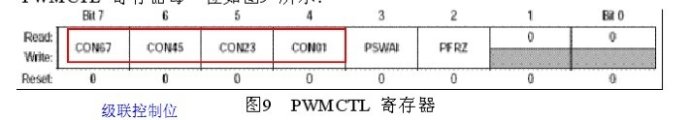

PWM使能寄存器。相应的每一位控制每一个通道。如果是级联方式,那么使能将由高通道的使能决定。比如

通道0和通道1级联成16位的PWM,那么这个级联的PWM的使能就由 PWME_PWME1 决定。

PWM时钟选择。0,1,4,5通道 PWMCLK_PCLK(0 or 1 or 4 or 5) =0 (则选择CLOCKA) =1 (则选择CLOCKSA)

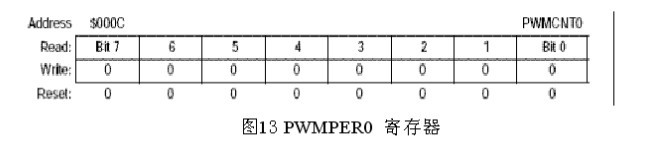

PWM时钟源预分频寄存器

分频系数的对照表格。 E 代表总线时钟,也就是前面PLL出来的 Bus Clock。

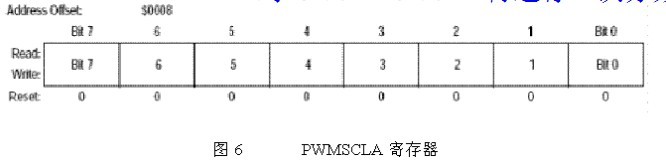

PWMSCLA寄存器实际上是对 前面已经对总线实行分频后的 ClockA 再次进行分频,从而得到更小的时钟源。

极性设置寄存器。0 表示 初始输出 点平。1 表示初始输出 高电平

PWM对齐方式设置寄存器。0 左对齐。1 中间对齐

PWM 控制寄存器。主要用于设置是否级联模式。若PWMCTL_CON01=1;则表示 通道0和1进行级联

PWM周期设置。 周期为

占空比设置寄存器。PWM模块中每个通道有一个8位的计数器,当计数值实时跟占空比中的值进行比较,一但相等,则将电平翻转,并且实时跟周期寄存器中的值进行比较,一旦相等则清零重新计数。

示意图:

调试心得:

1、关于程序中寄存器的书写。

一种是总线方式。比如PWME 寄存器。可以直接总线赋值。如PWME=0x01;也可以进行位赋值 如 PWME_PWME0=1;(注意不能直接写PWME0=1;)

2、级联方式时:级联方式就是为了扩展 周期、占空比的。因此两个通道的 8位周期、占空比寄存器就级联成了16位的周期、占空比寄存器。特别需要注意的是,此时的 这16位的寄存器的高8位 是低通道的8位寄存器。

比如01通道级联成的16位寄存器的高8位是通道0的8位。

飞思卡尔PWM调试笔 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)