P0.0——P0.7是

P0口的8位双向口线。第一功能为基本输入输出;第二功能是在系统扩展时,分时做为数据总路线和低8位地址

总线。

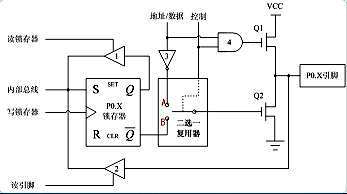

这里重点介绍一下P0口的结构及其工作过程:P0口的1位(例如:P0.0)结构如图

它由一个输出锁存器、两个三态锁存器(1、2)、输出控制电路(一个非门(3)、一个与门(4)、一个多路控制开关(MUX))、输出驱动电路(两只场效应管Q1、Q2)组成。

功能1:做基本I/O口使用

CPU发出的控制信号为低电平,使多路控制开关MUX接通B端,即与输出锁存器的“!Q”连接,同时使与门输出为低电平,场效应管Q1截止。

当P0输出数据时,写信号加在锁存器的R引脚上,内部总线上的数据通过S脚由锁存器的“!Q”端反相输出到Q2的栅极。若内部总线上数据为1,则Q2栅极上为0,此时Q2截止,Q2处于漏极开路的开漏状态,因此为了保证P0.0输出高电平,必须外接上拉电阻,否则P0端口不能正常工作 !若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

当P0输入数据时,分为读引脚和读锁存器两种方式,分别用到两个输入缓冲器。

读引脚操作,即单片机执行端口输入指令(如MOV A,P0)时的操作。这时由“读引脚”信号将三态缓冲器2打开,引脚上的数据经三态缓冲器2输入到内部总线。

读锁存器操作,即单片机执行“读—修改—写”类指令(如ANL A,P0)时的操作。在执行这类指令时,由“读锁存器”信号使三态锁存器1打开,读入P0口在锁存器中的数据,然后与累加器A中的数据进行逻辑运算,再反结果写回到P0口。这类操作不直接从P0口引脚上读入数据,而是从锁存器Q端读数据,其目的是为了防止出错,确保得到正确结果

功能2:系统扩展时分时做为数据总路线和低8位地址总线

此时控制信号为高电平,多路转换开关MUX接通A端,且与门的输出由“地址/数据”端的状态决定。

!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。