单片机IO口的上下拉电阻问题总结

时间:11-28

来源:互联网

点击:

上下拉电阻的问题,必须与IO口具体的内部结构相结合,才能分析清楚。

以下分析传统51单片机和AVR单片机的IO口。

51单片机

以下只分析P0和P1,其他类同。

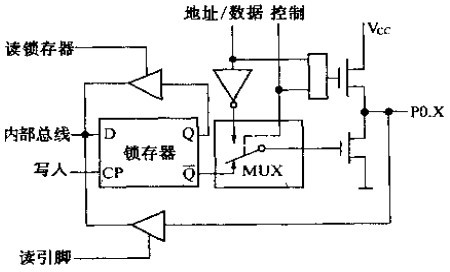

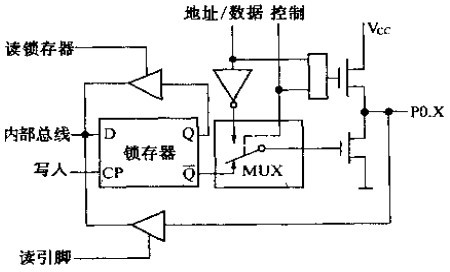

1.P0位结构图如下:

当P0作为通用IO口使用时,上面的场效应管会截止,可以理解成上边的电路断路,剩下电路仅为一开漏极电路。

输入时:引脚上的信号直接通过读引脚的缓冲器被读入;

输出时:由于上边的电路近似断路,剩下的电路为开漏极,所以需要加上上拉电阻才能输出高电平;

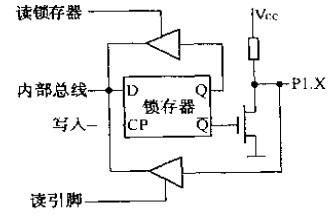

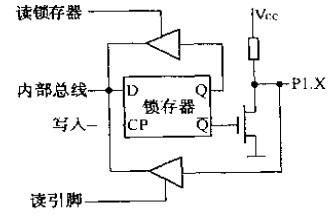

2.P1位结构图如下:

输入时:由于已带上拉电阻,所以需先将场效应管截止,即置1,才能正确读入;

输出时:由于已带上拉电阻,所以无需再加上拉电阻;

注:有时自带的上拉的电阻为弱上拉电阻(阻值很大,使得IO口的驱动电流不够),所以可以再外接强上拉电阻。

AVR单片机

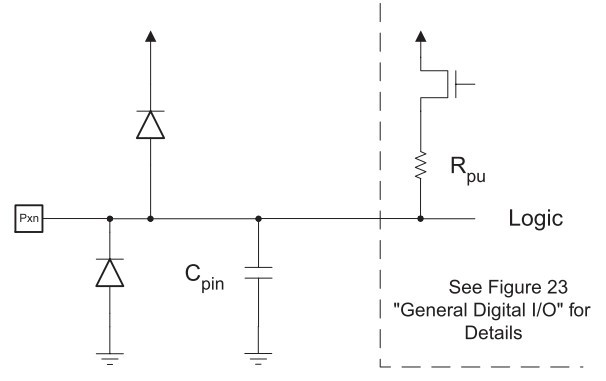

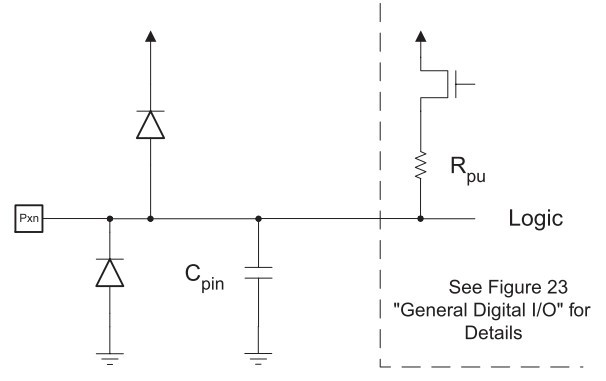

IO口等效原理图如下:

输入时:直接读入;

输出时:可自行配置是否使用内部上下拉电阻;

总结

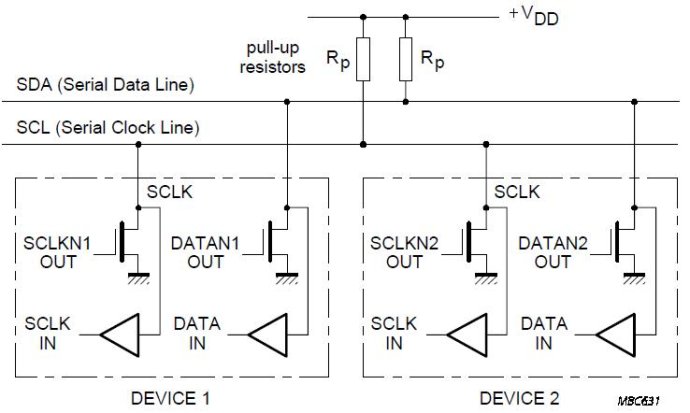

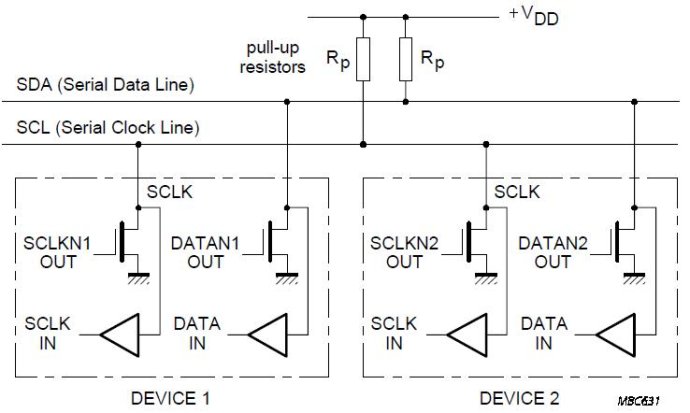

1.输入时,与上拉电阻关系不大;输出时,要根据需要选择使用自带或外部的上拉电阻。下图可帮助理解:

2.输出时,要考虑到输出高低电平时,IO口自身的拉出电流和灌入电流的大小限制,是否满足驱动外电路。

3.以上分析仅为帮助理解。

以下分析传统51单片机和AVR单片机的IO口。

51单片机

以下只分析P0和P1,其他类同。

1.P0位结构图如下:

当P0作为通用IO口使用时,上面的场效应管会截止,可以理解成上边的电路断路,剩下电路仅为一开漏极电路。

输入时:引脚上的信号直接通过读引脚的缓冲器被读入;

输出时:由于上边的电路近似断路,剩下的电路为开漏极,所以需要加上上拉电阻才能输出高电平;

2.P1位结构图如下:

输入时:由于已带上拉电阻,所以需先将场效应管截止,即置1,才能正确读入;

输出时:由于已带上拉电阻,所以无需再加上拉电阻;

注:有时自带的上拉的电阻为弱上拉电阻(阻值很大,使得IO口的驱动电流不够),所以可以再外接强上拉电阻。

AVR单片机

IO口等效原理图如下:

输入时:直接读入;

输出时:可自行配置是否使用内部上下拉电阻;

总结

1.输入时,与上拉电阻关系不大;输出时,要根据需要选择使用自带或外部的上拉电阻。下图可帮助理解:

2.输出时,要考虑到输出高低电平时,IO口自身的拉出电流和灌入电流的大小限制,是否满足驱动外电路。

3.以上分析仅为帮助理解。

单片机IO口上下拉电 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)