电阻频率响应测试实验

设备:电阻,面包板,STM32F103VE 试验板 , 示波器。

方法:将100R,1K,10K,1M电阻,分别以不同形式接入频率为1K,10K,1M,10M,的方波,观察其波形和区别。

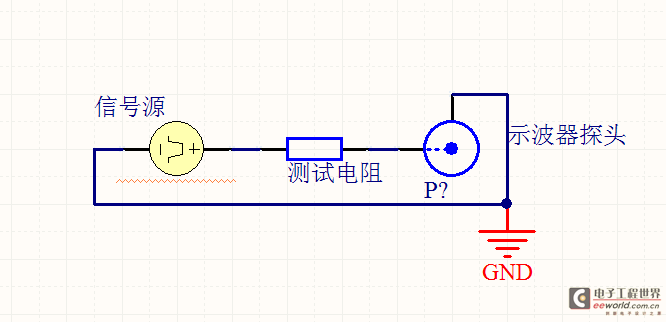

电路图:各种接发详见下文。

编译环境:iar

程序方面:采用定时器pwm模式,生成需要的频率以及占空比

#include "stm32f10x.h"

//#include

#include "key.h"

#include "SYSTICK.h"

void scan(void);

void init(void);

void main()

{

init();

GPIOC->CRL &=~ (0xff<0);

GPIOC->CRL |= (3<0)|(3<4);

GPIOC->ODR |= 0;

TIM5->ARR = 500 ;

TIM5->CCR1 = 250;

while(1)

{

scan();

}

}

void init()

{

SystemInit();

SYSTICK_Init(72);

RCC->APB2ENR |= (1<11) | (1<4) | (1<2) | (1<0); //打开pc pa和t1时钟

GPIOC->CRL &=~ (0xff<0);

GPIOC->CRL |= (1<3)|(1<7);

GPIOC->ODR |= (1<0)|(1<1);//按钮io初始化

GPIOA->CRH |= (11<0)|(11<4)|(11<8)| (11<12);//设置PA口为50M复用推挽输出

RCC->APB1ENR |= (1<3); //开启t5的时钟 led

RCC->APB2ENR |= (1<2)|(1<0);

TIM5->CR1 |= (0<4)|(1<7);//向上计数,使能重装载寄存器

TIM5->ARR = 20;//周期设置

TIM5->PSC = 0; //预分频设置

TIM5->CCMR1 &=~ ((3<8)|(3<0));////设置为ch1 ch2为输出模式

TIM5->CCMR1 |= (7<12)|(1<11)|(7<4)|(1<3); //pwm模式和输出比较预装载使能

TIM5->CCMR2 &=~ ((3<8)|(3<0));//设置为ch4 ch3为输出模式

TIM5->CCMR2 |= (7<12)|(1<11)|(7<4)|(1<3); //pwm模式和输出比较预装载使能

TIM5->CCER |= (1<12)|(1<8)|(1<4)|(1<0);//开启ch4输出

TIM5->CR1|=(1<0);

TIM5->CCR1 = 10;

GPIOA->CRL &=~ (0xf<0);

GPIOA->CRL |= (2<2)|(3<0);

GPIOA->CRL &=~ (0xf<4);

GPIOA->CRL |= (2<6)|(3<4);

GPIOA->CRL &=~ (0xf<8);

GPIOA->CRL |= (2<10)|(3<8);

GPIOA->CRL &=~ (0xf<12);

GPIOA->CRL |= (2<14)|(3<12);

}

void scan()

{

if(Scan_Mode())

{

TIM5->ARR = TIM5->ARR+100 ;

TIM5->CCR1 = TIM5->CCR1+50 ;

TIM5->EGR = 1;

}

if(Scan_Add())

{

TIM5->ARR = TIM5->ARR-50 ;

TIM5->CCR1 = TIM5->CCR1-25 ;

TIM5->EGR = 1;

}

}

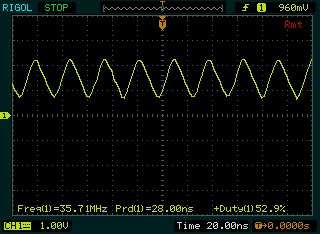

而且根据以上程序发现,IO的翻转速度可以达到36M,但基本上是严重变形了的

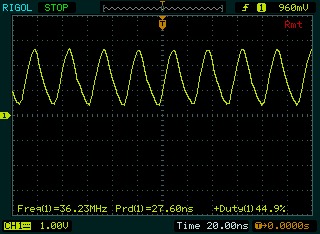

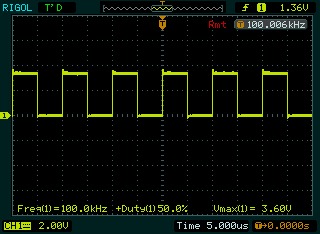

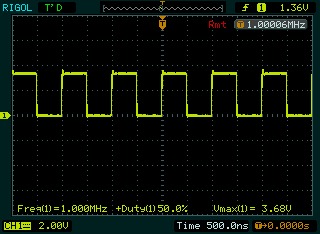

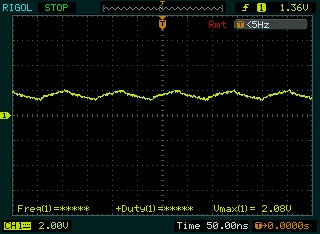

这是直接测量管角上的波形

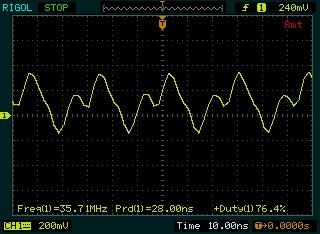

这是接了一块非常不好的导线,测量的波形

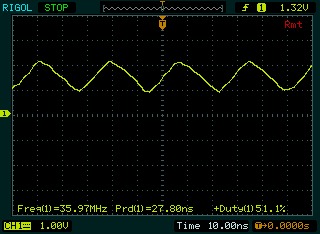

这是接了一般的导线,测量的波形

从上面的波形可以看出,导线的分布电容,和分布电阻对波形的影响还是挺大的。

估计要是产生36M的标准方波是没戏了,这也是我为啥要测试这些波形的原因。测试这些,可以对高频波形的预知,好对生成更好的更标准的波形做基础。

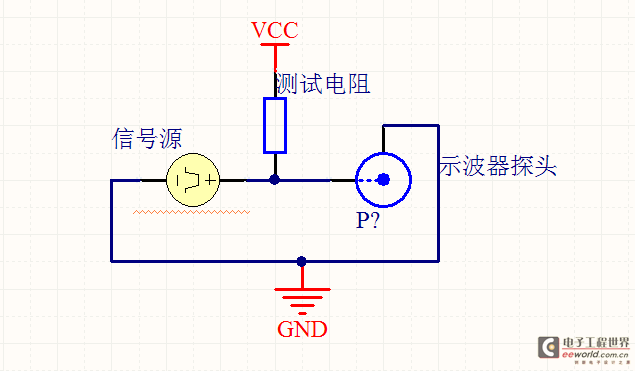

进入主题,开始测试,首先是电路图,最简单的

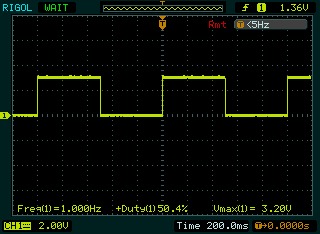

这是1HZ的,测试电阻,用1个10K和100K,波形,基本保持不变。

这是100HZ的波形,其测试电阻为100K,如果不仔细看,是看不到方波的右下角已经开始有一些小的变化了。

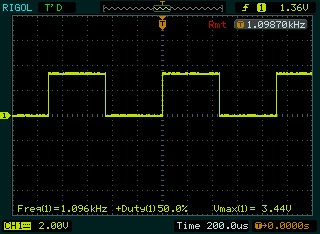

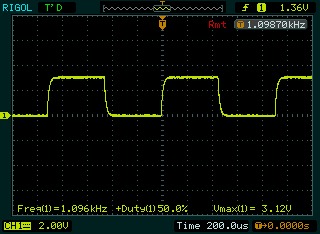

这是1KHZ的方波,第一幅图电阻为1K,而第二副图电阻为100K,可以明显的看到,波形开始扭曲。

100KHZ方波,测试电阻0欧,方方正正的,很好看

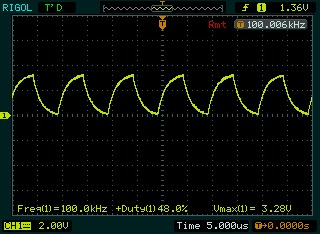

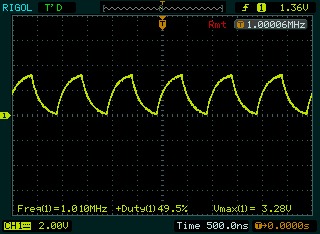

当测试电阻为10K时,波形已经变成这个鸟样子了,可以看到,图中的最大电压也从3.6V降到了3.28V

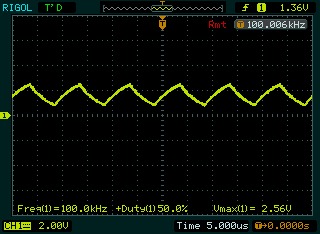

这是30K的样子,最大电压和最小电压都变了。

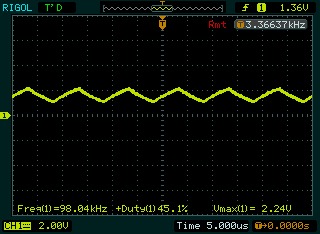

这是50K的样子,已经看不出原来波形的样子了,直接变成了很短的三角波了。看来这小小的电阻还是真厉害啊。

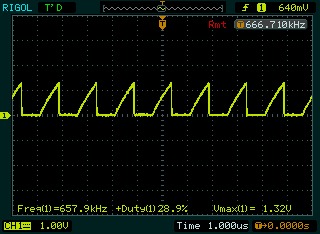

1MHZ 测试电阻为0欧,貌似还凑合

1K测试电阻,我怎么看,怎么想锯条,锯锯齿,锯锯齿的

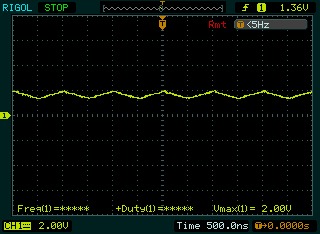

这是10K的测试电阻,已经快变成1条线了

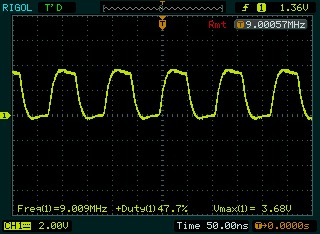

这是10MHZ的频率,测试电阻为0欧,啥也没加,就已经变形了

这个是10MHZ,1k测试电阻,就已经啥也没有了

从上面这个这些图可以看出,在低频情况下,长距离传输数据,信号畸变是小的,电阻的大小,对波形不构成太大影响

而超过1K频率时,电阻的增加是波形产生扭曲,而且信号频率越大,或者电阻越大,情况就越严重,而超过10Mhz的时候,1K的电阻就已经会使信号面目全非了。

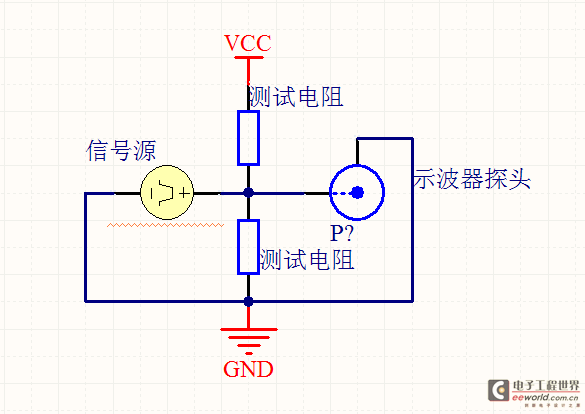

方案二:采用上拉电阻的形式,看看能不能矫正扭曲的波形呢?

在开漏模式下,试了一下10K上拉电阻,650K左右的频率,样子也蛮奇怪的,呵呵

这种图形,基本上不会给波形带来任何效果,试了一下,不好用。

只是电阻的话,估计不会给波形带来啥效果,要不,就不用那么复杂的电路了,其他的接入方法,就不试了,也没想出来还有啥方法,明天测试电容的。

电阻频率响应测试实验STM32F103V 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)