欲玩转Power Class 2?这些要点必须知!

为移动设备设计射频前端时,射频工程师始终面临着挑战。更多数量的频段(最多达到 40 个),包括 Wi-Fi 和蓝牙,都要在一个器件上共存,SKU(最小存货单位)也更少— 这些要求都让设计变得非常棘手。有些情况下,难以实现的共存要求不只是给设计带来些许不便,而是会成为一场恶梦。但这种情况只是在 Power Class 2(下称PC2)等新标准发布之前存在。

PC2:TD-LTE 新标准

PC2 是一种新的 LTE 功率标准,在 2016 年 12 月通过 3GPP 认证,它是一项增加高性能用户设备 (HPUE) 和改进全球 2.5 GHz LTE TDD 覆盖面的行业计划的一部分。频率较高的信号无法传输得很远,因此蜂窝网络运营商需要一种能够提高功率输出的方法。PC2 能够满足这一需求。

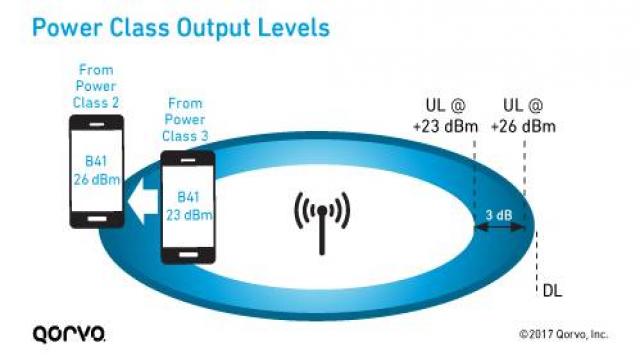

作为以前的标准,Power Class 3(下称PC3)的 3GPP 规范将移动设备到基站塔的频段 41 上行链路限定为 23 dBm 标称输出功率。这种定义有助于确保向后兼容以前的技术 (GSM/UMTS),让网络部署拓扑能够保持相似。

但是,TDD-LTE 频段 41 没有关联任何 3GPP 旧版技术,因此它无需保持后向兼容性。这使 3GPP 能够定义一种新的功率标准—— Power Class 2 ——并提高 TDD 频段 41 的功率输出。

PC2 允许输出功率级别达到 26 dBm——这是 PC3 以前定义的最大输出功率的两倍(如下图所示)。

输出功率增加至 PC2,可以补偿更高 TDD 频率下的更大传播损耗,让运营商能够维持基站覆盖面,而无需增加成本昂贵的基础设施。对于用户体验和运营商而言,这将是一个双赢的局面——但对器件制造商而言,这是一大挑战。

PC2 射频挑战

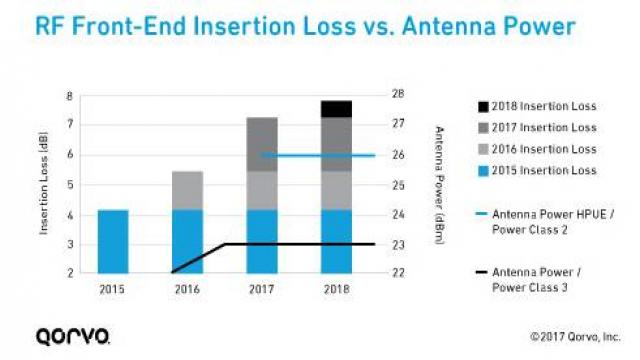

随着射频前端复杂性提高,整体插入损耗链路预算也会增加。在设计时采用传统分立元件和多余的匹配,只会增加链路预算。新的 PC2 要求(即输出功率达到 26 dBm)让射频设计变得更加复杂。

设计前端时,射频工程师需要使用:

-

最佳链路预算,满足 26 dBm 的新 2 级功率标准

-

设计技术和元件,抑制插入损耗的逐年增加(参见下图)

-

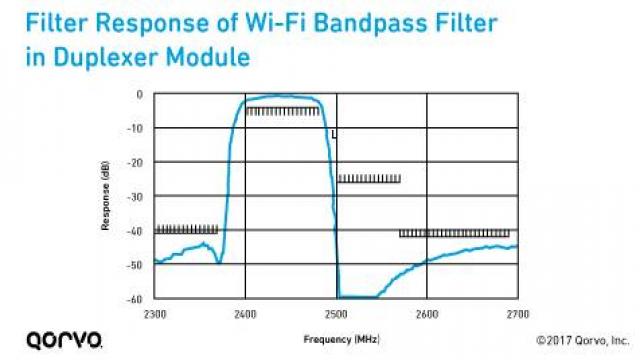

最佳滤波器,减少射频共存问题

但新标准也带来了益处。从射频前端模块的角度看,分析表明,26 dBm 功率的 TDD B41 实际上可以降低功率放大器功耗,有利于延长电池寿命。另外,在频段 41 TD-LTE 中,基站覆盖面最多可扩大 30%。

Qorvo 如此满足 PC2 标准

作为射频设计工程师,我们必须尽可能降低这些匹配损耗和系统链路预算。Qorvo 利用两种策略实现这个目标:

-

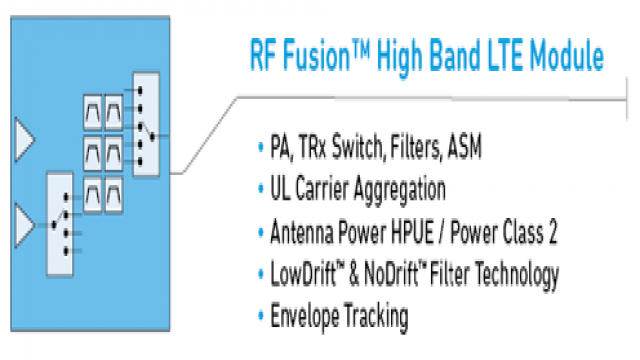

集成模块:高性能、高集成度的射频模块,例如 Qorvo 的RF Flex™和RF Fusion™,实现了滤波器、开关、功率放大器之间的直接匹配,从而将 Tx 和 Rx 路径的匹配损耗降低多达0.5 dB。这有助于设计人员更加接近26 dBm 输出的目标,而不是将所有负担都放到功率放大器输出上。

-

高级滤波器技术:射频滤波器可以减少共存问题,但也给系统设计带来了插入损耗。滤波技术面临的挑战是既要传输所需的信号,同时又要衰减不需要的频谱成分。Qorvo 的BAW滤波器技术提供更大的滤波器衰减和出色的滤波器插入损耗,这是避免干扰和优化 B41 链路预算所必需的。

总 结

随着频段增加和频率提高,外加载波聚合等容量解决方案的扩充,射频前端设计将变得更加困难。PC2 标准是一大挑战,但如果与技术实力最雄厚的射频产品供应商开展合作,射频工程师仍然可以从容应对。使用高性能的 Qorvo BAW 滤波器技术和高度集成的设计方法,例如 RF Flex™ 和 RF Fusion™,手机设计人员能够在更短时间内更高效地设计产品。

Power Class 2 射频工程师 移动设备 相关文章:

- RF MICRO DEVICES扩展业界领先的PowerSmart产品系列(03-07)

- 引领 2017 研发潮流的手机热点大预测:Power Class 2(01-16)

- 引领2017研发潮流的手机热点大预测:Power Class 2(02-16)

- 基于PEX8648交换芯片的数据处理模块设计(08-18)

- 基于RFID的航空食品物流信息管理平台(12-20)

- 基于FPGA的嵌入式串行千兆以太网设计(12-05)