讨论s3c2440的时钟与DMA

时间:12-02

来源:互联网

点击:

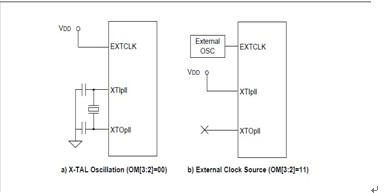

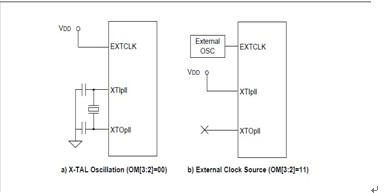

s3c2440的时钟与电源管理模块包括3个部分,时钟控制,USB控制和电源控制。时钟源如下图有两个,左边的是外部晶振提供,右边是外部时钟提供。

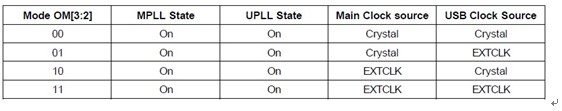

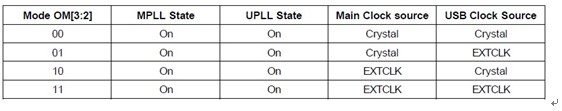

由这个表可以看出来时钟源的选择是在引导的时候由OM[3:2]引脚决定的。

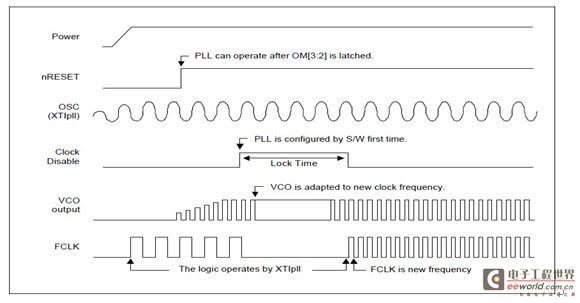

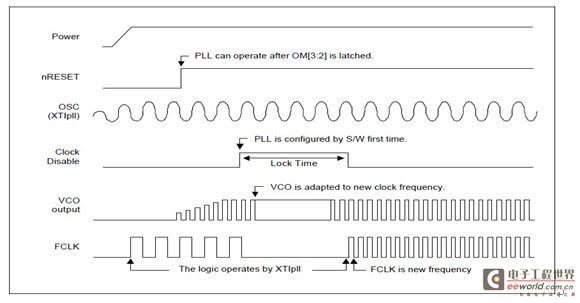

如图,刚上电一小段时间后,FCLK=晶振时钟,等待4个时钟周期后,PLL锁存有效,自动插入一段PLL Lock Time,即PLL锁定时间,此时,FCLK停止震荡,CPU停止工作,Lock time的长短由寄存器LOCKTIME设定。PLL Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

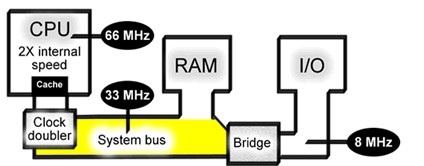

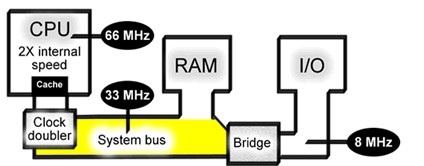

有两个PLL,一个是MPLL,一个是UPLL。MPLL分频得到FCLK(用于CPU),HCLK(用于AHB BUS),PCLK(用于APB BUS)。UPLL产生UCLK给USB提供48M或96M时钟。上边的是s3c2440a的体系结构图,最上边的是CPU wrapper,也就是CPU核,中间的AHB BUS相当于系统总线,APB相当于IO总线。中间的Bridge相当于康柏(Compaq)公司提出的南桥。这个Bridge的作用就是连接高速和低速总线。这种结构类似于:

通过配置MPLLCON的Mdiv,Pdiv,Sdiv可以获得MPLL。通过公式:

Mpll = (2 * m * Fin) / (p * 2S)

m = (Mdiv + 8), p = (Pdiv + 2), s = Sdiv

AHB BUS(advanced high-performance bus)上连接的是高速设备如LCD,USB Host,ExtMaster,SDRAM等。注意他们是通过控制器间接跟总线连接的。APB BUS(advanced peripherals bus)连接的就是低速的外围设备。

DMA对s3c2440的性能非常重要。S3c2440支持位于系统总线和外围总线之间的4个通道的控制器。每个DMA控制器通道无限地执行系统总线上的设备或外设总线上的设备之间数据搬移。

DMA有3种状态:

状态一:作为初始状态,DMA等待DMA请求,一旦请求到达,进入状态二,在此状态,DMA ACK和INT REQ都为0。

状态二:在此状态,DMA ACK变成1且计数器(CURR_TC)从DCONN[19:0]装载。注意DMA ACK直到后边被清除一直保持1。

状态三:在此状态,进行DMA原子操作的子状态机被初始化。此子状态机从源地址读取数据并写入目的地址。此操作应该考虑数据大小和传输大小(single or burst),而在全服务模式whole service mode中,次操作一直被重复直到计数器(CURR_TC)变成1;而在单服务模式single service mode中,此操作仅被执行一次。当计数器(CURR_TC)变成0且外部中断设置DCON[29]

寄存器被置1,主状态机发出中断请求信号(INT REQ)。另外,遇到以下情况,其清除DMA ACK。

(1)在全服务模式下计数器(CURR_TC)变成0

(2)在单个服务模式下计数器原子操作完成

外部DMA请求/应答模式:

有3种类型的外部DMA请求/应答协议(单服务请求,单服务握手和全服务请求模式)。

请求模式和服务模式的对比:

-如果XnXDREQ 保持有效,下个传输马上开始,否则它会一直等到XnXDREQ 有效。

握手模式

如果XnXDREQ 无效,DMA 在两个周期内将XnXDACK 设无效。否则他会一直等

XnXDREQ 无效。

当需要DDMA操作的时候,外部DMA请求引脚XnXDREQ置为低电平,此时,DMA控制器向CPU发出占用总线的请求,当总线请求成功后,XnXDACK变为低电平,表示CPU已将总线使用权交给了DMA控制器,可以进行数据传输。当数据传输完成后应答信号XnXDACK置为高电平,通知CPU完成一次数据传输。

由这个表可以看出来时钟源的选择是在引导的时候由OM[3:2]引脚决定的。

如图,刚上电一小段时间后,FCLK=晶振时钟,等待4个时钟周期后,PLL锁存有效,自动插入一段PLL Lock Time,即PLL锁定时间,此时,FCLK停止震荡,CPU停止工作,Lock time的长短由寄存器LOCKTIME设定。PLL Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

有两个PLL,一个是MPLL,一个是UPLL。MPLL分频得到FCLK(用于CPU),HCLK(用于AHB BUS),PCLK(用于APB BUS)。UPLL产生UCLK给USB提供48M或96M时钟。上边的是s3c2440a的体系结构图,最上边的是CPU wrapper,也就是CPU核,中间的AHB BUS相当于系统总线,APB相当于IO总线。中间的Bridge相当于康柏(Compaq)公司提出的南桥。这个Bridge的作用就是连接高速和低速总线。这种结构类似于:

通过配置MPLLCON的Mdiv,Pdiv,Sdiv可以获得MPLL。通过公式:

Mpll = (2 * m * Fin) / (p * 2S)

m = (Mdiv + 8), p = (Pdiv + 2), s = Sdiv

AHB BUS(advanced high-performance bus)上连接的是高速设备如LCD,USB Host,ExtMaster,SDRAM等。注意他们是通过控制器间接跟总线连接的。APB BUS(advanced peripherals bus)连接的就是低速的外围设备。

DMA对s3c2440的性能非常重要。S3c2440支持位于系统总线和外围总线之间的4个通道的控制器。每个DMA控制器通道无限地执行系统总线上的设备或外设总线上的设备之间数据搬移。

DMA有3种状态:

状态一:作为初始状态,DMA等待DMA请求,一旦请求到达,进入状态二,在此状态,DMA ACK和INT REQ都为0。

状态二:在此状态,DMA ACK变成1且计数器(CURR_TC)从DCONN[19:0]装载。注意DMA ACK直到后边被清除一直保持1。

状态三:在此状态,进行DMA原子操作的子状态机被初始化。此子状态机从源地址读取数据并写入目的地址。此操作应该考虑数据大小和传输大小(single or burst),而在全服务模式whole service mode中,次操作一直被重复直到计数器(CURR_TC)变成1;而在单服务模式single service mode中,此操作仅被执行一次。当计数器(CURR_TC)变成0且外部中断设置DCON[29]

寄存器被置1,主状态机发出中断请求信号(INT REQ)。另外,遇到以下情况,其清除DMA ACK。

(1)在全服务模式下计数器(CURR_TC)变成0

(2)在单个服务模式下计数器原子操作完成

外部DMA请求/应答模式:

有3种类型的外部DMA请求/应答协议(单服务请求,单服务握手和全服务请求模式)。

请求模式和服务模式的对比:

-如果XnXDREQ 保持有效,下个传输马上开始,否则它会一直等到XnXDREQ 有效。

握手模式

如果XnXDREQ 无效,DMA 在两个周期内将XnXDACK 设无效。否则他会一直等

XnXDREQ 无效。

当需要DDMA操作的时候,外部DMA请求引脚XnXDREQ置为低电平,此时,DMA控制器向CPU发出占用总线的请求,当总线请求成功后,XnXDACK变为低电平,表示CPU已将总线使用权交给了DMA控制器,可以进行数据传输。当数据传输完成后应答信号XnXDACK置为高电平,通知CPU完成一次数据传输。

s3c2440时钟DM 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)