SJA1000硬件电路设计

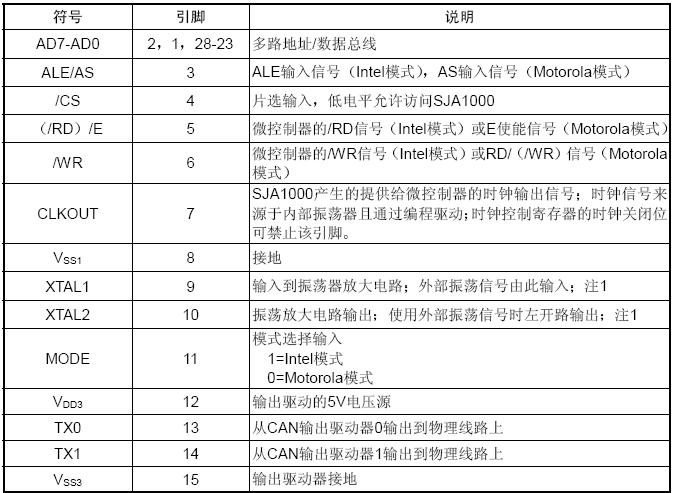

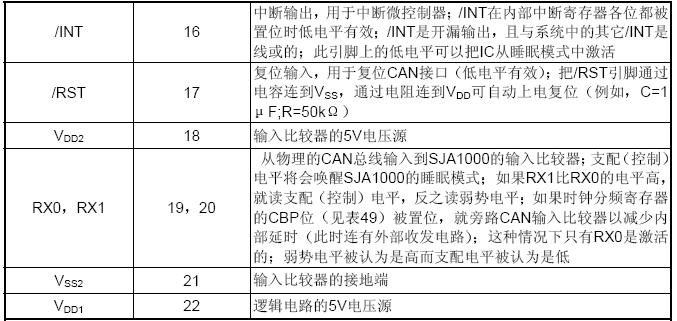

各个管脚的符号功能什么的上面的表里介绍的很详细,我就不多废话了。

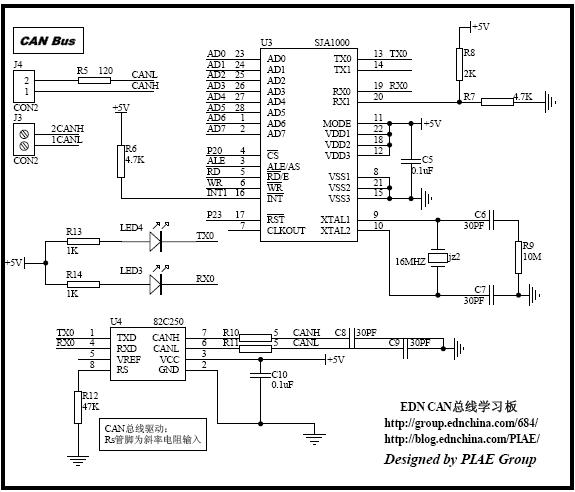

接着我们看SJA1000的这些管脚在实际电路中是怎么进行连接的,因为只谈SJA1000的硬件电路设计,所以就截一张PIAE提供的电路原理图里关于SJA1000的部分。

下面我们要具体解析这个电路图。

AD0-AD7是地址/数据复用总线。因为这个电路是把SJA1000做外部RAM扩展了,所以它的电路连接也势必要符合外部RAM的连接要求。(特权同学也是第一次接触单片机的外部存储器扩展应用,所以开始的时候也很是纳闷,然后拿起课本一阵恶补后才恍然大悟。)先补一下外部扩展RAM的知识,然后再谈这个电路就容易多了:51单片机外部RAM的扩展最多是可以寻址64KB的,也就是最多可以有16条地址线来寻址,P0口是低八位地址扩展口,P2口是高八位地址扩展口。如果外部RAM不需要用到全部16条地址线(SJA1000就只有8条地址线),那么只要把低位地址线和外部RAM的相应地址线连接,高位的地址线在寻址时都默认为1,比如这里的SJA1000,它的8条地址线是和P0口相连接的,所以对SJA1000的寄存器寻址时的地址应该是FF00H-FFFFH,但是为什么PIAE提供的程序里的地址定义却是FE00H-FEFFH呢?这就要讨论CS信号的连接问题了,我们知道,CS是片选输入信号,只有当它是低电平时才能访问SJA1000。再看看它和谁连了?是P2.0口,正好是地址线高八位的最低位,如果按常理来说,寻址FF00H,那么P2.0就是高电平,SJA1000就不能被访问。所以寻址FE00H时才选通SJA1000,这时才是SJA1000寄存器的地址。

上面讨论了寻址的问题,只是就事论事,如果还不理解,我建议找本书详细了解下单片机的外部存储器的扩展后就会明白的。另外,我们知道单片机的P3.0和P3.1有第二功能,就是做RD和WR用,所以它们就和外部寄存器(这里指SJA1000)的RD和WR相连接了。单片机的ALE脚和存储器的ALE脚也必须相连接。以上的这些连接使得SJA100成为了单片机的外部存储器。

再看INT脚是和单片机的INT1相连,也就是作为接收中断信号来告诉单片机接收到了新的数据帧。RST脚是复位脚,接P2.3成为可编程的。

TX0\RX0连接82C250的对应脚,数据帧是通过这两个脚传送出去的(具体的工作原理可以参考82C250的资料,这里就不讨论了)。MODE脚接正,说明工作在INTER模式下。XTAL1和XTAL2两个脚接16MHz的晶体,SJA1000的工作是有一定的时序的,它可以完成数据的发送以及数据的校验等功能,这完全是IC设计者考虑的东西,我们只要了解它的工作原理,通过单片机配置SJA1000的工作方式,并且向SJA1000写数据或者读数据就可以达到CAN总线通信的目的了。

SJA1000硬件电 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)