基于FPGA技术的RS232接口时序电路设计

1 发送逻辑电路的设计

1.1 时序近似

RS 232接口可选的波特率如9 600b/s,115.2 Kb/s等同11.059 2 MHz的时钟有着整数倍的关系,但通常情况下提供FPGA的时钟大多采用频率为40~80 MHz,同11.059 2 MHz之间存在一定的时序误差。

例如一个由1个起始位,8个数据位,1个停止位组成,假定串行信号的波特率为9 600b/s,则每个位的时序时间为:

104 166.666 666 666 666 666 666 666 666 67 ns

相当于80 MHz计数器计数到:

8 333.333 333 333 333 333 333 333 333 333 3舍去小数部分。

由80 MHz驱动的计数器产生时序时每个字符误差为4.166 666 666 666 666 666 666 666 666 666 7 ns。这样由10个字符组成的一次发射时序误差约为41.7 ns小于1/1 000可以忽略不计。

1.2 发送时序设计

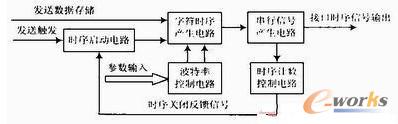

RS 232接口的时序电路由启动电路、字符产牛电路、同步时钟产生电路。波特率控制电路,和时序关闭电路组成。发送时序电路原理框图如图1所示。

图1 发送时序电路原理框图

1.3 发送电路原理描述

以波特率为9 600b/s的时序为例,在发送数据之前,系统微处理器将相应波特率参数锁存在FPGA内部的波特率控制电路的寄存器内(由触发器构建),使每次输出的字符同步信号的周期为104.167μs(对应波特率9 600b/s)。

当系统发出发送启动信号时,字符时序电路以每个字符104.167μs的速率在预发射数据的逻辑电平控制之下输出时序信号,同时在时序中插入停止位和起始位字符信号。

在完成上述发送时序的过程中,时序计数控制电路会检测发送时序的工作状态,当检测每次时序的停止位完成输出后,时序计数控制电路会发出时序关闭反馈信号,使电路回复到预发射的初始工作状态,并等待处理器再次触发时序电路和对数据参数的重置。

2 接收逻辑电路的设计

2.1 接收时序设计

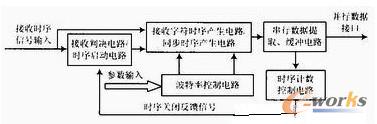

接收时序电路原理框图如图2所示。

图2 接收时序电路原理框图

2.2 接收电路原理描述

以波特率为9 600b/s的时序为例,在接收数据之前系统微处理器将相应波特率参数锁存在FPGA内部的波特率控制电路的寄存器内(由触发器构建),使每次输出的字符位同步信号的周期为104.167 μs(对应波特率9 600b/s)。字符位同步信号是接收电路存储接收数据逻辑状态的关键。作为同步时钟信号,该信号可驱动接收到的串行数据电平输入移位寄存器内并锁存。

当系统接收到一帧串行信号时,首先要判断是否是新的一帧数据,接收判决电路通过对输入串行信号的起始位字符脉宽进行裁决,按照RS 232接口通信协议在某一特性波特率下,一帧信号的起始是一定脉宽的负脉冲。通过计数器可以检测到负脉冲的起始时间和脉冲宽度,当脉冲宽度达到某一数值时启动接收时序。

接收时序电路会通过被记录下的接收信号的准确到达时间,推算出每个串行数据位对应的时序时刻,从而输出对应每个位中间时刻的字符位同步信号(脉冲)作为接收移位寄存器的同步时钟信号驱动移位寄存器对接收数据电平的记录。

被锁存的数据通过并行总线被系统微处理器提取。这一过程可以通过对处理器的中断实现,但需要接收时序电路在完成数据接收后立即产生一个中断信号,通知处理器提取接收数据。

接收时序计数器会对接收时序时间进行检测,当接收时序到达结束时刻时,其输出的时序关闭反馈信号会使接收电路恢复到初始工作电路,等待下一帧数据的到达。

3 结论

通过FPGA实现RS 232接口时序逻辑电路,已经在工程实践过程中实现了接口标准规定的全部功能。可以认为,通过FPGA的逻辑电路设计可以完全取代专用芯片。介于FPGA的可塑性和灵活性,可以通过相应逻辑电路设计实现包括以太网,USB、RS 485等常见的数据接口。

FPGA技术RS232接口时序电 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)