片上总线Wishbone 学习(四)总线周期之复位操作

总线周期概述

一个总线周期由多个不可分的时钟周期构成,完成单次读/写操作、块读/写操作或者读改写操作。总线周期也分为单次读/写周期、块读/写周期和读改写周期。一次块读/写总线周期完成多次数据读/写操作。一般情况下,一次操作由主设备和从设备控制信号间的一次握手,以及同时进行的地址和数据总线的一次传输构成。块操作表示整个操作需要完成多次数据传送。在总线周期中主设备和从设备预先设定好的共同遵守控制信号握手规则,以及地址和数据总线的传输规则称作总线协议。

在以后的文章中,所给图例中给出的信号均为主设备的输入输出信号。因此,对操作的描述也从主设备信号的角度展开,以便于对照正文理解图例。比如"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到主设备的输入信号DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的响应。"的等价描述为:"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到其输出信号DAT_O()和TGD_O(),将输出信号ACK_O置高作为对主设备STB_O的响应。"

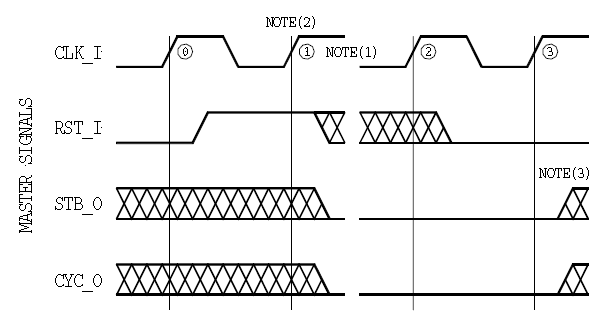

复位操作

图 1

片上总线Wishbone总线周期复位操 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)