异步周期结束方式

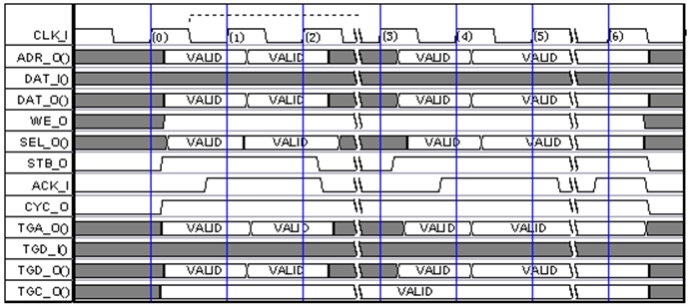

块写操作的例子如图1所示。图1的一次块写操作由五个相互关联的单次写操作完成。

在时钟上升沿0,主设备将地址信号ADR_O()、TGA_O()放到总线上,将数据信号DAT_O()、TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作正在进行,将STB_O置高表示第一次写操作开始。

在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿1,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第一次写操作完成,于是将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作继续在进行,将STB_O置高表示第二次写操作开始。

在时钟上升沿2到达之前,从设备检测到主设备发起的第二次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿2,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第二次写操作完成,发现自己的数据还没有准备好,于是将STB_O置低表示插入等待周期。

在时钟上升沿3到达之前,从设备检测到STB_O为低,也将ACK_I置低。

在时钟上升沿3,主设备发起第三次操作,将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作继续进行,将STB_O置高表示第三次写操作开始。

在时钟上升沿4到达之前,从设备检测到主设备发起的第三次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿4,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第三次写操作完成,于是将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将STB_O继续置高表示第四次写操作开始。

在时钟上升沿5到达之前,从设备检测到主设备发起的第四次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿5,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第四次写操作完成,于是发起第五次操作,将新地址信号ADR_O()、新TGA_O()放到总线上。

在时钟上升沿5之后新的时钟上升沿到达之前,从设备发现因为某些原因暂时无法继续接收数据,因此将ACK_I信号置低,插入等待。

在时钟上升沿6,当从设备发现可以继续接收数据,于是在在最后一个等待周期结束且上升沿5到达之前,将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第五次写操作完成。并将STB_O和CYC_O置低表示整个块写操作完成。

图1 Wishbone总线的块写操作(异步周期结束方式)

同步周期结束方式

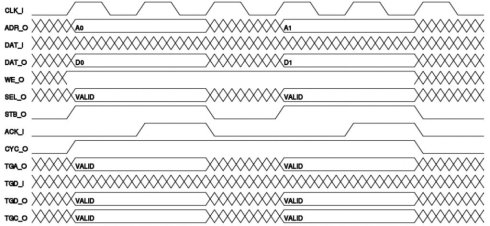

图2 Wishbone总线的块写操作(同步周期结束方式)

在时钟上升沿0:

- Master在[ADR_O()]和[TGA_O()]发出有效的地址

- Master在[DAT_O()]和[TGD_O()]发出数据

- Master发出[WE_O],表明是一个写周期

- Master发出有效数据选择信号[SEL_O()]表明哪些数据是有效的

- Master发出[CYC_O]和[TGC_O()]表明总线周期的开始

- Master发出[STB_O]表明操作的开始

注意:Mater必须在时钟上升沿1或之前发出[CYC_O]和/或[TGC_O()]

在时钟上升沿1:

- Slave检测到主设备发起的操作,准备发出[ACK_I]

- Slave准备锁存[DAT_O]和[TGD_O()]

- Slave发出[ACK_I]应答[STB_O]

在时钟上升沿2:

- Slave锁存[DAT_I]和[TGD_I()]

- Master拉低[STB_O]插入等待周期(-WSS-)

在时钟上升沿3:

- Master在[ADR_O()]和[TGA_O()]发出有效的地址

- Master在[DAT_O()]和[TGD_O()]发出数据

- Master发出[WE_O],表明是一个写周期

- Master发出有效数据选择信号[SEL_O()]表明哪些数据是有效的

- Master发出[CYC_O]和[TGC_O()]表明总线周期的开始

- Master发出[STB_O]表明第二次操作的开始

在时钟上升沿4:

- Slave检测到主设备发起的操作,准备发出[ACK_I]

- Slave准备锁存[DAT_O]和[TGD_O()]

在时钟上升沿5:

- Master监视[ACK_I]

- Master拉低[STB_O]和[CYC_O],结束总线周期