时钟振荡器:古老而又复杂的一项技术

在过去的几年里,我一直在参与无线电设计,所有这些都需要时钟振荡器。也许你已经知道了锁相环(PLL)和不知道它的参考时钟是如何产生的。或者,也许你已经读过一本关于晶体振荡器和质疑,如果你真的只需要只是一个晶体管和一些无源器件来创建一个。如果你有,跟随本系列里我将讨论在使用无线电频率参考和一些实用的系统和设计考虑涉及。

频率参考是一个无线电的一个重要部分。一个重要的功能是提供一个输入时钟到PLL允许无线电接收和发射在一个精确的频率。满足蓝牙低功耗(BLE)标准规定的基准频率精度为+/-50ppm(百万分之一),Zigbee为+/-40ppm。此外,蓝牙低功耗规范要求的初始传输的中心频率精确到+/-75KHZ。如果发射机的频率精度不够,那么接收机就接不到数据了。40ppm意味着什么呢?想象一下用一天时间来数秒,最多只能有四秒的误差,看起来非常精确,但实际上相对另外一些标准还差得很远。比如对于GSM手机和基站之间的通信来说,相当于连续数数115天,但最多只能有一秒的误差。

如何获得这一精准的频率呢?利用PLL锁相环,这是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

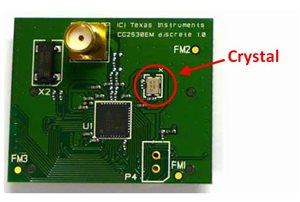

如上图所示,CC2530评估模块套件中红色圆圈处。

第一个晶体振荡器距离现在已将近百年时光,尽管已经是一个非常成熟的技术,但如何权衡仍然是值得思考的问题:比如您当前的设计标准是什么?您知道您的设计需要满足什么样的精度要求?等等。

http://e2e.ti.com/blogs_/b/connecting_wirelessly/archive/2013/11/06/frequency-references-101.aspx

更多关于晶振相关内容,请访问TI无线连接。

晶 相关文章:

- 基于DSP实现的LCD液晶屏显示技术(06-04)

- 基于DSP的晶闸管数字触发器的研究与设计(01-20)

- 64位MIPS的起源,回顾及展望(11-02)

- 基于PROTEUS技术的ARM7显示系统设计与仿真实现(11-22)

- uC/GUI在S3C44B0X的移植及其在数据显示系统中的应用(02-15)

- 基于DSP和单片机通信的液晶显示设计方案(07-20)