工程师教你如何设计D类放大器

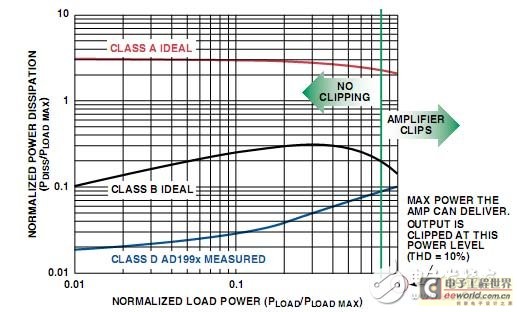

率与扬声器提供的负载功率(PLOAD)之间的关系。其中负载功率相对最大负载(PLOAD max)功率水平归一化,箝位的正弦波信号保证10%总谐波失真(THD)。图中的垂直线表示PLOAD开始箝位的位置。

图4. A类、B类放大器和D类放大器输出级的功耗比较

可以看出,对于多种负载其功耗明显不同,尤其是在高端和中端值负载条件下。在箝位开始之初,D类放大器输出级的功耗约是B类放大器的1/2.5,是A类放大器的1/27。应当注意,消耗在A类放大器输出级的功率比传递到扬声器的功耗大,这是使用大的DC偏置电流的结果。

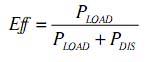

输出级功率效率Eff定义如下:

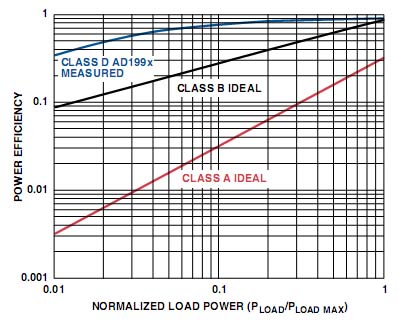

在箝位开始之初,A类放大器的Eff= 25%,B类放大器的Eff=78.5%,D类放大器的Eff=90%(见图5)。对于A类放大器和B类放大器,这些最佳例证经常在教科书中引用。

图5. A类、B类和D类放大器输出级的功率效率比较

功耗和功率效率的差异在中等功率水平处很大。这对于音频很重要,因为大音量音乐的长期平均功率水平要比达到PLOAD max的瞬时峰值水平低很多(为其1/5到1/20,取决于音乐类型)。因而,对于音频放大器,[PLOAD = 0.1×PLOAD max] 是一个合理的平均功率水平,按照这个功率水平评估PDISS。在这个功率水平,D类放大器输出级的功耗是B类放大器的1/9,是A类放大器的1/107。

对于10 W PLOAD max的音频放大器,1 W的平均PLOAD认为是保真音频功率水平。在这种条件下,D类放大器输出级内部功耗为282 mW,对于B类放大器为2.53 W,对于A类放大器为30.2 W。在这种情况下,D类放大器的效率从高功率条件下的90%减少到78%。但即使是78%也要远优于B类放大器和A类放大器,它们的效率分别为28%和3%。

这些差别对于系统设计具有重要的影响。对于1 W以上的功率水平,线性输出级的过大的功耗要求采用有效的散热方法以避免不可接受的发热,通常是使用大金属板作为散热板,或用风扇促进放大器空气散热。如果放大器是集成电路(IC),就可能需要大尺寸、高成本的增强散热封装以促进热传导。这些考虑在消费类产品中很麻烦,例如平板电视,其印制电路板面积(PCB)面积很宝贵,或汽车音响,其发展趋势是在固定空间内增加通道数。

对于1 W以下的功率水平,处理浪费的功率可能比处理散热还困难。如果是电池供电,线性放大器输出级消耗电池电荷要比D类放大器快。在上面的例子中,D类放大器输出级耗费的电源电流是B类放大器的1/2.8,是A类放大器的1/23.6,因此它们用于蜂窝电话,PDA和MP3播放器等产品在电池的寿命方面有很大差别。

迄今为止,我们为了简单起见,只是专门注重放大器输出级的分析。但是当考虑放大器系统中所有功耗时,线性放大器要比低输出功率D 类放大器更有利。原因是在低功率水平条件下,产生和调制开关波形所需要的功率会很大。因而,精心设计的低中功率的AB类放大器的宽系统静态功耗优势使得它们可与D类放大器相竞争。虽然对于宽的输出功率范围,毫无疑问D类放大器具有低功耗优势。

D类放大器术语以及差分方式与单端方式的比较

图3示出D类放大器中输出晶体管和LC滤波器的差分实现。这个H桥具有两个半桥开关电路,它们为滤波器提供相反极性的脉冲,其中滤波器包含两个电感器、两个电容器和扬声器。每个半桥包含两个输出晶体管,一个是连接到正电源的高端晶体管MH,另一个是连接到负电源的低端晶体管ML。图3中示出的是高端pMOS晶体管。经常采用高端nMOS晶体管以减小尺寸和电容,但需要特殊的栅极驱动方法控制它们(见深入阅读资料1)。

全H桥电路通常由单电源(VDD)供电,接地端用于接负电源端(VSS)。对于给定的VDD和VSS,H桥电路的差分方式提供的输出信号是单端方式的两倍,并且输出功率是其四倍。半桥电路可由双极性电源或单极性电源供电,但单电源供电会对DC偏置电压产生潜在的危害,因为只有VDD/2电压施加到过扬声器,除非加一个隔直电容器。

“激励”的半桥电路电源电压总线可以超过LC滤波器的大电感器电流产生的标称值。在VDD和VSS之间加大的去耦电容器可以限制激励dV/dt的瞬态变化。全桥电路不受总线激励的影响,因为电感器电流从一个半桥流入,从另一个半桥流出,从而使本地电流环路对电源干扰极小。

音频D类放大器设计因素

虽然利用D类放大器的低功耗优点有力推动其音频应用,但是有一些重要问题需要设计工程师考虑,包括:

? 输出晶体管尺寸选择

? 输出级保护

? 音质

? 调制方法

? 抗电磁干扰( EMI)

? LC滤波器设计

? 系统成本

输出晶体管尺寸选择

选择输出晶体管尺寸是为了在宽范围信号调理范围内降低功耗。当传导大的IDS时保证VDS很小,要求输出晶体

D类放大器音频放大器工程 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)