《Cortex-M0权威指南》之体系结构---存储器系统

时间:12-23

来源:互联网

点击:

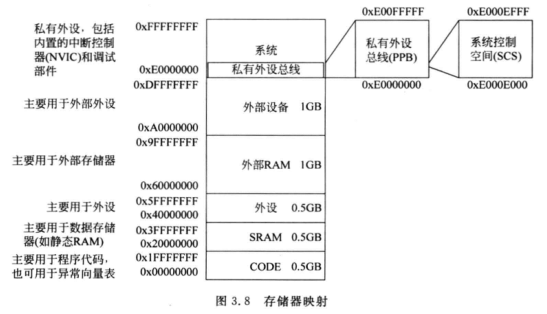

Cortex-M0处理器为32位处理器,所以具有最大4G的寻址空间。在体系结构上,存储器空间被划分位一系列的区域,每个区域都有推荐的用途,以提高不同设备间的可移植性。

M0处理器内置了各种不见,例如NVIC和一些调试部件,它们都被映射到系统空间的固定地址上。因此所有基于M0的设备在中断控制和调试方面,都由相同的编程模式。这种处理有利于软件移植,也方便调试工具提供商位M0的微控制器和片上系统SOC提供开发调试方案。

Cortex-M0支持大端和小端操作,使用相应的配置即可选择,但已经成型的设计不能在两者切换。

Cortex-M0存储器系统和外设由微控制器提供商和片上系统SOC设计者提供,因此基于Cortex-M0的产品的存储器就存在各种大小和类型。

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- DSP与普通MCU的比较(02-23)

- TMS320C32的存储器接口设计(10-29)

- FM18L08在DSP系统中的应用(01-23)